The increasing demand for data communication throughput between system components has driven the requirement for faster SerDes IP data rates. The complexity of the transmit (Tx) and receive (Rx) signal conditioning functions has correspondingly evolved. As a result, the simulation methodology for SerDes electrical interface… Read More

Griffin Securities’ Jay Vleeschhouwer on EDA Acquisitions and StartupsJay Vleeschhouwer, Managing Director of Software Research at…Read More

Griffin Securities’ Jay Vleeschhouwer on EDA Acquisitions and StartupsJay Vleeschhouwer, Managing Director of Software Research at…Read More Security Coverage: Assuring Comprehensive Security in Hardware DesignAs hardware systems become increasingly complex and security…Read More

Security Coverage: Assuring Comprehensive Security in Hardware DesignAs hardware systems become increasingly complex and security…Read More Scaling 3D IC Technologies – Siemens Hosts a Meeting of the Minds at DAC3D IC was a very popular topic at…Read More

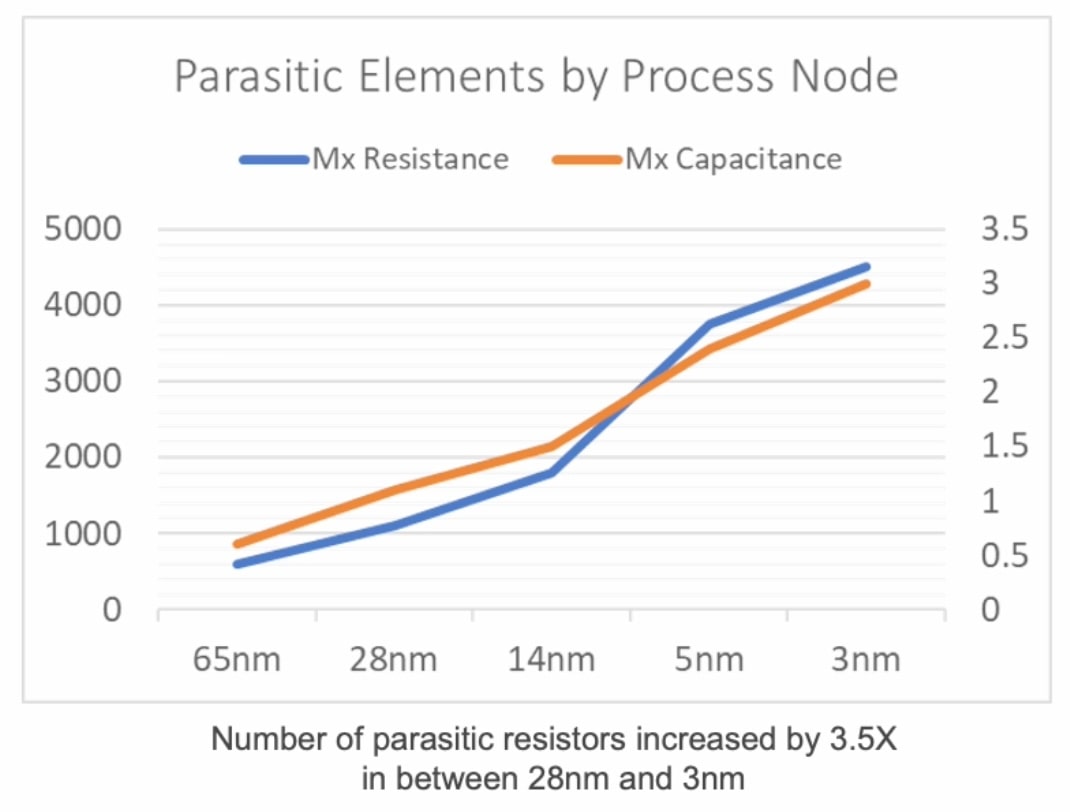

Scaling 3D IC Technologies – Siemens Hosts a Meeting of the Minds at DAC3D IC was a very popular topic at…Read More Analysis and Exploration of Parasitic EffectsWith advanced semiconductor processes continuing to shrink, the…Read More

Analysis and Exploration of Parasitic EffectsWith advanced semiconductor processes continuing to shrink, the…Read More Siemens Proposes Unified Static and Formal Verification with AIGiven my SpyGlass background I always keep an…Read More

Siemens Proposes Unified Static and Formal Verification with AIGiven my SpyGlass background I always keep an…Read MoreThe Cloud-Edge Debate Replays Inside the Car

I think we’re all familiar with the cloud/edge debate on where intelligence should sit. In the beginning the edge devices were going to be dumb nodes with just enough smarts to ship all their data to the cloud where the real magic would happen – recognizing objects, trends, need for repair, etc. Then we realized that wasn’t the best… Read More

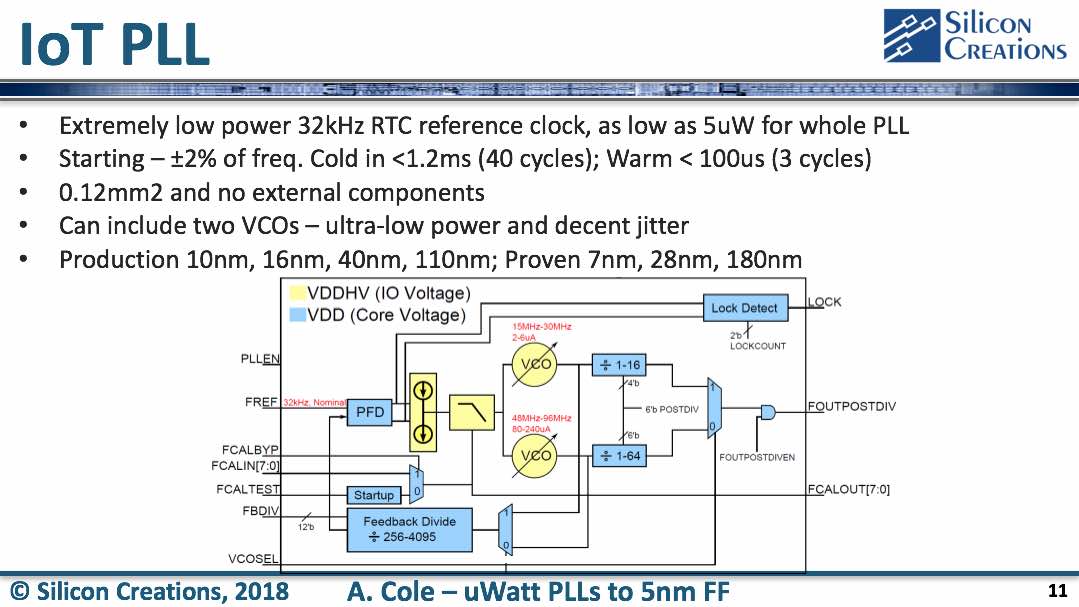

Essential Analog IP for 7nm and 5nm at TSMC OIP

When TSMC’s annual Open Innovation Platform Exposition takes place, you know it will be time to hear about designs starting on the most advanced nodes. This year we were hearing about 7nm and 5nm. These newer nodes present even more challenges than previous nodes due to many factors. Regardless of what kind of design you are undertaking… Read More

Webinar: ASIC and FPGA Functional Verification Study

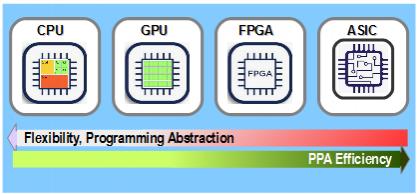

ASIC or FPGA? Each design style has earned designers’ votes depending on the level of urgency, application complexity and funding of their assigned projects. While it is feasible to transition from ASIC to FPGA design or vice versa, such a move is usually done across project refresh instead of midcourse.

Trade war could be the tipping point for American manufacturing

When Western companies moved manufacturing to China, it was all about minimizing costs. China was a developing country with labor costs among the lowest in the world. It also offered massive subsidies and readily turned a blind eye to labor abuse and environmental degradation.

Today, China is the world’s second-largest economy… Read More

The Latest in Parasitic Netlist Reduction and Visualization

The user group events held by EDA companies offer a unique opportunity to hear from designers and CAD engineers who are actually using the EDA tools “in the trenches”. Some user presentations are pretty straightforward – e.g., providing a quality-of-results (QoR) design comparison when invoking a new tool feature added to a recent… Read More

TSMC Q3 2018 Earnings Call Discussion!

The TSMC OIP Forum was very upbeat this year and now we know why. It wasn’t long ago that some media outlets and a competitor said 7nm would not be a popular node because it is too expensive blah blah blah. People inside the fabless semiconductor ecosystem however know otherwise. As I have said before, 7nm will be another strong node … Read More

ASML most immune to slow down due to lead times Not LRCX

ASML reported EUR2.78B in revenues with EUR2.08B in systems. 58% was for memory. EUV was EUR513M with 5 systems. Importantly orders were for EUR2.20B in systems at 64% memory and 5 EUV tools. This was likely better than expectations given the overall industry weakness. EPS of EUR1.60 was more or less in line with expectations. Guidance… Read More

Portable Stimulus enables new design and verification methodologies

My usual practice when investing is to look at startup companies and try to understand if the market they are looking to serve has a significant opportunity for a new and disruptive technology. This piece compiles the ideas that I used to form an investment thesis in Portable Stimulus. Once collected, I often share ideas to get feedback.… Read More

Honey I Shrunk the EDA TAM

The “20 Questions with Wally Rhines” series continues

Throughout the history of the EDA industry, pricing models have caused discontinuities in the way the industry operates. For a variety of competitive reasons, individual companies have developed ways to change the pricing model in an attempt to secure competitive… Read More

Musk’s new job as Samsung Fab Manager – Can he disrupt chip making? Intel outside