SRAM is the workhorse for on-chip memories, valued for its performance and easy integration with standard processes. The needs of wearable, IoT and AI SOCs have put a lot of pressure on the requirements for all on-chip memories. This is perhaps most evident in the area of power. AI chips that rely heavily on SRAM register files are being developed for use in cameras and voice recognition systems that must be always-on. Wearables and IoT devices need SRAM register files for secure communications, analog tuning and rapid real time processing. A white paper by Tony Stansfield, CTO at sureCore Limited, discusses how they have developed a process independent power optimized architecture for delivering register file IP.

To meet the traditional needs of SRAM, the emphasis had focused on area and performance optimization. The newer applications now driving the market call for a shift toward placing a much higher priority on power. The key to lowering power requirements are found in bit cells and peripheral circuits performing read and write operations. SureCore lays out in their white paper the methods they use in their SRAM architecture to achieve significantly low dynamic and static power.

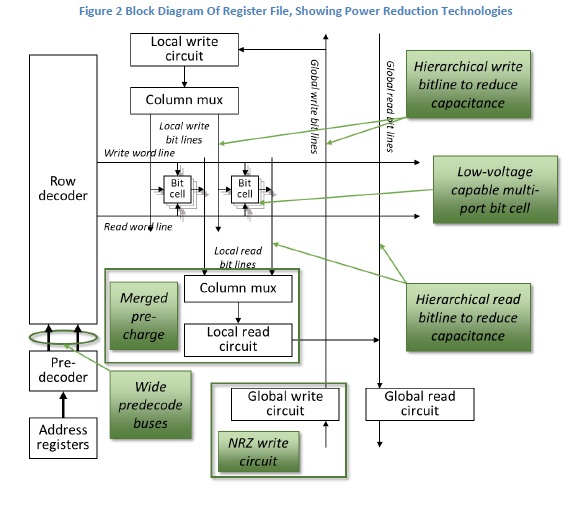

An important aspect they mention is that register files are much more deeply integrated into logic circuits than larger SRAM blocks. As a result, they ideally need to use the same supply lines as the surrounding logic circuits. Because SRAM bit cells are more voltage sensitive than CMOS logic, an effective power reduction strategy must address this. The approach that sureCore took involves redesigning the bit cells so they can run at lower voltages. They then go further and change their bit cell so that it has separate read and write bit lines. This reduces the need for voltage assist and improves performance. Monte Carlo and High-Sigma simulation are used by sureCore to verify that the bit cells will operate at the necessary PVTs.

Using their experience in building low power SRAM blocks, they apply many of the same techniques to their register file design. To reduce capacitance on long wires, such as bit lines, they use hierarchical partitioning. To minimize activity on long wires they apply wide pre-decoding of addresses. Their patented ‘cascode pre-charge sense’ circuits help reduce voltage line swing, which helps reduce active and leakage power. The paper also goes into details on how they take advantage of the separate read and write lines to further optimize circuit performance.

The sureCore paper cites third party benchmarking that shows just how much power can be saved with their IP. They suggest that dynamic power savings of around 75% can be realized. Also, because their IP can operate over a wide range of voltages, low power modes can be more easily used to minimize power.

In many rapidly expanding markets power saving has moved up to the number one priority. Even when faced with areas versus power trade-offs, power is now often the overriding design criteria. The sureCore SRAM IP, especially for use in SRAM register files, provides significant power savings through their well thought out architecture. The white paper makes interesting reading and offers more detail about their offering. It is available for download on their website.

About sureCore

sureCore is the Low Power leader that empowers the IC design community to meet their aggressive power budgets through a portfolio of innovative, ultra-low power memory design services and standard products. sureCore’s low-power engineering methodologies and design flows helps you meet your most exacting memory requirements with customized low power SRAM IP and low power mixed signal design services that create clear marketing differentiation. The company’s low-power product line encompasses a range of down to near-threshold silicon proven, process-independent SRAM IP.

Also Read:

CEO Interview: Paul Wells of sureCore

Low Power Design – Art vs. Science

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.