The semiconductor ecosystem is changing. Monolithic design is becoming multi-die design. Processors no longer inform software development options. It’s now the other way around with complex AI software informing the design of purpose-built hardware. And all that special-purpose hardware needs drivers to make it come to life. This interplay of complex, multi-chip connectivity and ever-increasing demands of how the software invokes the hardware are all new. This isn’t your father’s (or mother’s) chip design project. All of this made me wonder where the driving forces will be to take us to the next level of semiconductor system design. There are many important players in this field. Recently, I was struck by a series of observations about one of those players. The apparent alignment is noteworthy. In this post, I’ll explore those observations. Is Arteris poised to enable next generation system design?

Some Observations

Most folks think “network on a chip”, or NOC when they hear the name Arteris. The company has certainly blazed an important trail toward automating the interconnect of vast on-chip resources. That is the beginning of the story and not the end, however. Providing the backbone to connect the parts of a complex design opens many doors. Let’s look at a few.

One is the “memory wall” problem. While collections of CPUs and GPUs deliver huge amounts of performance, the memories that manage critical data for those systems lag in performance. And they lag a lot – many orders of magnitude. This is the memory wall problem.

A popular approach to dealing with this issue is to pre-fetch data and store it in a local cache. This way is far faster – a few CPU cycles vs. over 100 CPU cycles. It’s a great approach, but it can be tricky to ensure the right data is in the right place at the right time, and consistent across all caches. Systems that effectively deliver this solution are called cache coherent, and achieving this goal is quite difficult.

Arteris has developed a cache-coherent NOC to address this challenge. That’s one obstacle out of the way. You can learn more about this Arteris solution here.

Another challenge is just keeping track of the huge list of IPs used in contemporary designs. Tasks here include ensuring the right IP is deployed, and all stakeholders have up-to-date information and keeping track of the various configurations and derivatives. Current designs can contain 500+ up to 1K IP blocks with 200K+ up to 5M+ registers. Challenges this creates include:

- Content integration from various sources (soft IP, configurable third-party IP, internal legacy

- Design manipulation (derivative, repartitioning, restructuring)

There are many formats used to keep track of all this. Spreadsheets, DOCX, IP-XACT, and SystemRDL are a few examples. Again, Arteris has a well thought out solution to this problem. Levering its Magillem technology, these problems can be tamed. You can learn more about this Arteris solution here.

And I’ll examine one more. How to keep track of all the data required to orchestrate the interface between all that complex software and the hardware that brings those software innovations to life. This is typically called the hardware/software interface, or HSI.

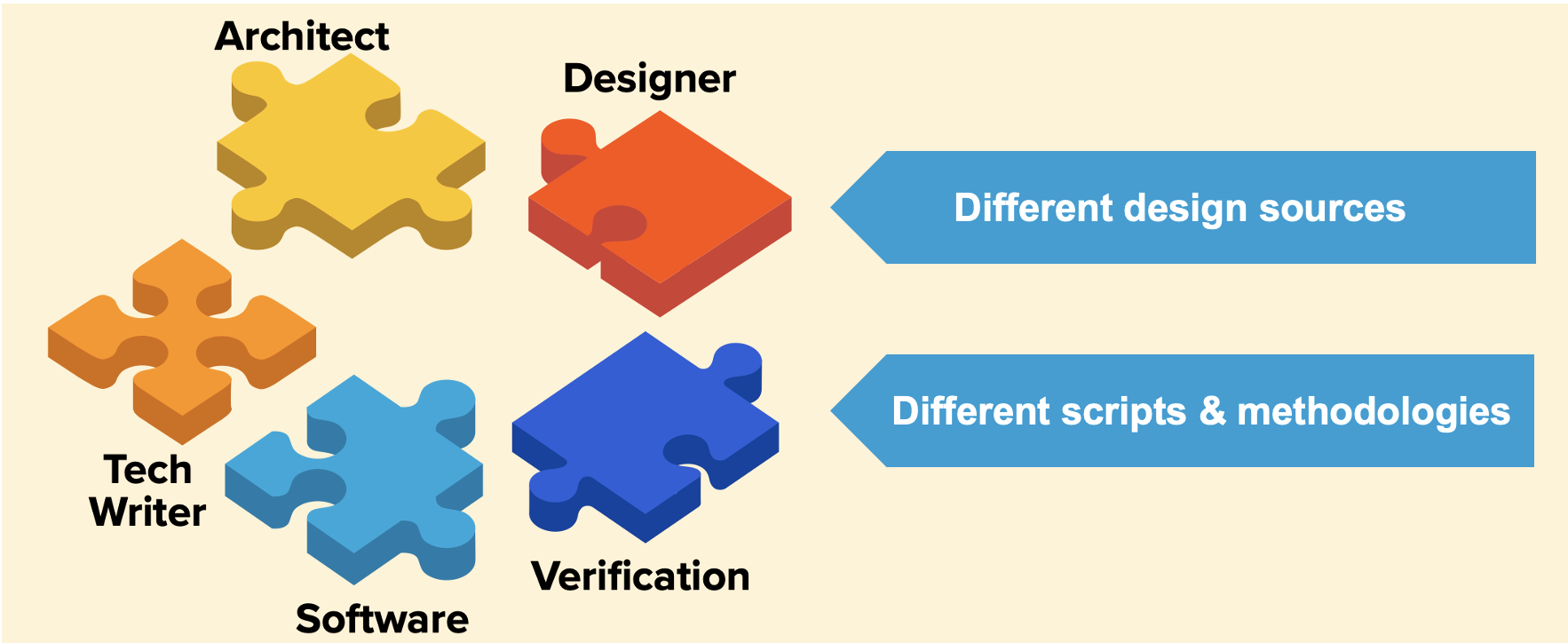

This problem has many dimensions. Not only is it complex, but the formats needed by all stakeholders are different. That is, folks like RTL architects, software developers, verification engineers and technical publication staff all need their own version of this information in a specific format. Generating all that information in lockstep and conveying the same design intent in different formats is not easy.

In a past life, I worked with a company called that had a very well thought out way of dealing with these challenges. What happened to Semifore? If you guessed they are now part of Arteris, you would be right. More technology to knock down more of the obstacles to achieve next generation designs. The core tool for Semifore is called CSRCompiler, and the diagram below will give you a sense of what it can do.

There is a lot more to be said here, but you get the idea.

What’s Next?

I’ve just scratched the surface, highlighting some high-profile challenges that must be tamed to get to the next level of semiconductor system design. It turns out Arteris has mainstream technology to address all of them. They are a NOC company, and a lot more.

There are other challenges to be met of course. IP-XACT is an important element of advanced system design. This standard, also known as IEEE 1685, is an XML format that defines and describes reusable IP to facilitate its use in chip designs. IP-XACT was created by the SPIRIT Consortium as a standard to enable automated configuration and integration through tools and evolved into an IEEE standard.

There is a new version of this standard called IEEE 1685-2022. This new version contains a lot of additional functionality. It will be important for any company who aims to enable next generation system design to support these new capabilities. A partial list of what’s new includes:

- Removed conditionality

- Added XML document to describe memory element definitions

- Added mode-dependent memory and register access

- Added mapping from ports to register fields

- Added register field aliasing and broadcasting

- Added power domains and power domain bindings

Even though there are new challenges on the horizon, I have an optimistic view of how Arteris can help. In an Electronic Design article, Insaf Meliane, Product Management & Marketing Manager at Arteris stated:

The ever-evolving landscape of semiconductor chip design necessitates effective communication between design teams. The HSI serves as the bridge, and while challenges persist due to differing languages and requirements, tools like the CSRCompiler help simplify the process.

The methodology automatically documents changes across entire functional teams to deliver a reliable, up-to-date specification. It provides a single-source specification for register and memory-map information, fully configured for all teams in the formats and views they require.

This gives me more confidence in the Arteris approach to these problems. Is Arteris poised to enable next generation system design? I think the answer is YES, and I can’t wait to see what’s next.

Also Read:

Arteris Raises Bar Again with AI-Based NoC Design

MCUs Are Now Embracing Mainstream NoCs

Arteris Empowering Advances in Inference Accelerators

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.