Building a complex SoC is a risky endeavor that demands careful planning, strategic decisions, and collaboration across hardware and software domains. As highlighted in Darren Jones’ RISC-V Summit presentation from Andes Technology, titled “From Blueprint to Reality: Navigating SoC Tradeoffs, IP, and Ecosystem,” the journey from conceptual design to functional silicon involves navigating numerous tradeoffs while leveraging intellectual property and a supportive ecosystem. This process is not just technical but also strategic, ensuring that the final product meets performance, power, and cost goals while incorporating unique innovations, what Darren calls the “Secret Sauce.”

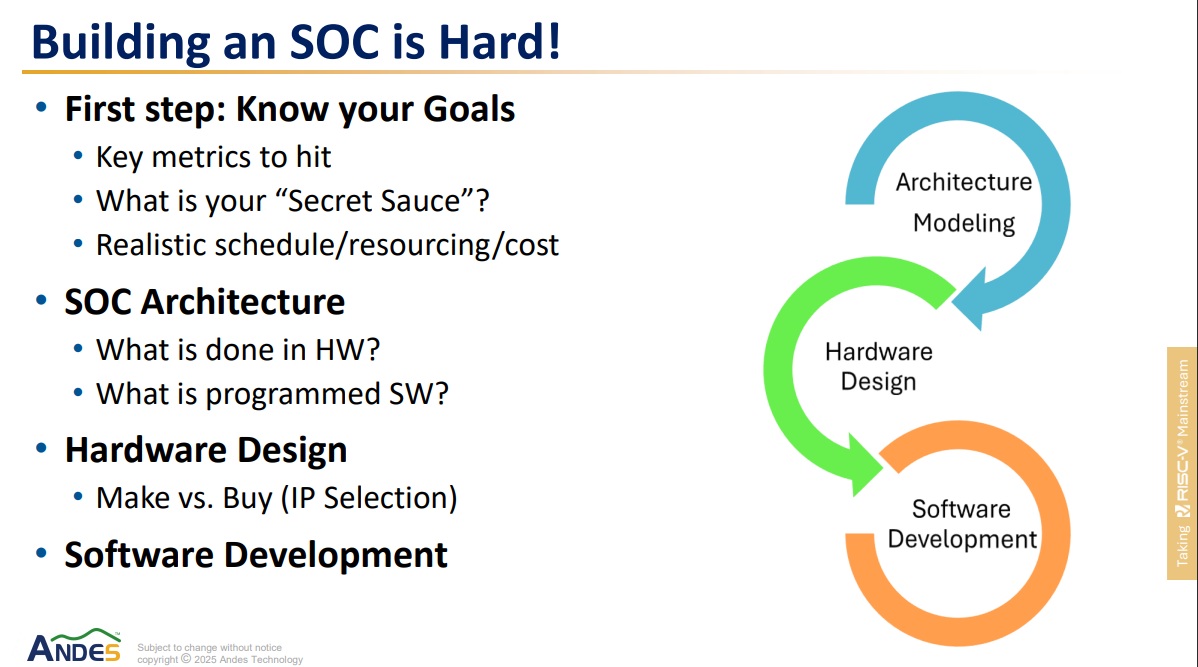

The first step in SoC development is defining clear goals. Engineers must identify key metrics such as performance benchmarks, power efficiency, area constraints, and market timelines. Understanding the “Secret Sauce” that distinctive feature setting the SoC apart, like advanced AI acceleration or ultra-low power consumption is crucial. A realistic assessment of schedule, resources, and costs prevents overruns. For instance, underestimating integration time can derail projects, as SoCs often combine custom logic with third-party IP.

SoC architecture forms the foundation, deciding what functions are implemented in hardware versus software. Hardware handles time-critical tasks like signal processing, while software offers flexibility for updates. This partitioning affects everything from power usage to scalability. Darren emphasizes modeling the architecture early to simulate tradeoffs, using tools like SystemC for high-level abstraction.

Hardware design involves critical choices: make or buy. Developing custom blocks in-house allows tailoring but increases risk and time. Buying IP, particularly processor cores, accelerates development. Darren focuses on processor IP selection, stressing hardware considerations like Power, performance and Area (PPA). Bus interface compatibility ensures seamless integration, such as with AXI or AHB standards. Customization is key in RISC-V ecosystems, where extensions like vector processing or custom operations enable the “Secret Sauce.” Questions like “Can your vendor enable features you didn’t think possible?” underscore the need for flexible partners.

Proper IP deliverables are non-negotiable: RTL code, testbenches for verification, documentation, and IP-XACT for metadata. Models range from fast instruction-set simulators for software development to cycle-accurate ones for timing validation and SystemC for system-level simulation. Product support and quality silicon-proven designs from reputable vendors mitigate risks. Andes Technology, a leader in RISC-V IP, exemplifies this with their AndesCore CPUs, which support coherent multi-core setups with features like platform-level interrupt controllers and L2 cache managers.

Software considerations are equally vital, often overlapping with hardware choices. Development tools, compilers, and IDEs must support the architecture. Operating system availability, Linux for complex applications, RTOS for real-time systems, or bare-metal for simplicity affects portability. Legacy code porting requires compiler compatibility, while application and firmware development demands efficient toolchains. Third-party code integration, such as DSP or neural network libraries, enhances functionality. Debug tools, including JTAG interfaces and software profilers, are essential for troubleshooting.

Collaboration with IP vendors is a recurring theme. Engaging early facilitates architecture discussions, customization, and benchmarking. Vendors like Andes provide PPA data and models to validate designs. Deliverables empower success: run the testbench to verify IP, read docs thoroughly, and use models for co-simulation. Product support prevents wasted effort. Darren advises contacting vendors promptly and building relationships for ongoing assistance.

In practice, these elements form an ecosystem where tradeoffs are inevitable. Prioritizing power might sacrifice performance, or customization could inflate costs. Successful SoCs, like those in IoT devices or automotive systems, balance these through iterative modeling and vendor partnerships. Andes’ tools, such as their DNN use-case models for neural networks, illustrate how integrated ecosystems support applications from frame capture to AI inferencing.

Bottom Line: Navigating SoC development requires a holistic approach. By knowing goals, architecting wisely, selecting robust IP, addressing software needs, and fostering vendor collaborations, teams can turn blueprints into reality. As Jones concludes, this ecosystem-driven strategy not only mitigates challenges but unlocks innovation, ensuring competitive edges in a fast-evolving semiconductor landscape.

Also Read:

The RISC-V Revolution: Insights from the 2025 Summits and Andes Technology’s Pivotal Role

Beyond Traditional OOO: A Time-Based, Slice-Based Approach to High-Performance RISC-V CPUs

Andes Technology: Powering the Full Spectrum – from Embedded Control to AI and Beyond

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.