Although version 2.0 of the Computer Express Link (CXL) standard is just making it into new designs, the next generation, version 3.0, has been approved and is now ready for designers to implement the new silicon and firmware needed to meet the new standard’s performance specifications. CXL, an open industry-standard interconnect, defines an industry-supported Cache-Coherent Interconnect for Processors, Memory Expansion and Accelerators. (For more about the CXL standard, check out the CXL Consortium website – www.computeexpresslink.org.)

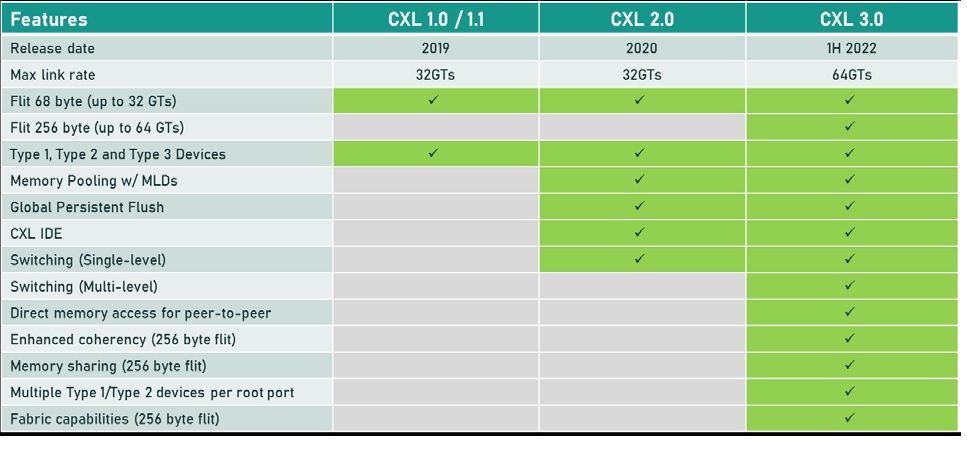

The CXL Consortium is an open industry standard group that was created to develop technical specifications that enable companies to deliver breakthrough performance for emerging usage models. Also able to support an open ecosystem for data-center accelerators and other high-speed enhancements, the standard offers coherency and memory semantics using high-bandwidth, low-latency connectivity between host processor and devices such as accelerators, memory buffers, and smart I/O devices. The updated standard (version 3.0) provides a range of advanced features and benefits including doubling bandwidth with the same latency (see the table).

To help speed the design of the new chips need to implement CXL 3.0, Avery Design Systems has developed verification IP (VIP) and virtual platform solutions supporting verification for the first wave of CXL 3.0 designs. As explained by Chris Browy, vice president sales/marketing of Avery, “we can enable leading developers of server processors, managed DRAM and storage class memory (SCM) buffers, switch/retimer, and IP companies to rapidly meet the growing needs for the CXL datacenter ecosystem in 2022 and beyond. Our collaboration with key ecosystem companies allows Avery to deliver best-in-class, robust CXL 3.0 VIP solutions that streamline the design and verification process and foster the rapid adoption of the CXL standard by the industry. Our CXL virtual platform and VIP co-simulation enables complete CXL system-level bring-up of SoCs in a linux environment.”

To help speed the design of the new chips need to implement CXL 3.0, Avery Design Systems has developed verification IP (VIP) and virtual platform solutions supporting verification for the first wave of CXL 3.0 designs. As explained by Chris Browy, vice president sales/marketing of Avery, “we can enable leading developers of server processors, managed DRAM and storage class memory (SCM) buffers, switch/retimer, and IP companies to rapidly meet the growing needs for the CXL datacenter ecosystem in 2022 and beyond. Our collaboration with key ecosystem companies allows Avery to deliver best-in-class, robust CXL 3.0 VIP solutions that streamline the design and verification process and foster the rapid adoption of the CXL standard by the industry. Our CXL virtual platform and VIP co-simulation enables complete CXL system-level bring-up of SoCs in a linux environment.”

Avery provides a complete System Verilog/UVM verification solution including models, protocol checking, and compliance test suites for PCIe® 6.0 and CXL 3.0 for CXL host, Type 1-3 devices, switches, and retimers. The verification solution is based on an advanced UVM environment that incorporates constrained random-traffic generation, robust packet-, link-, and physical-layer controls and error injection, protocol checks and coverage, functional coverage, protocol analyzer-like features for debugging, and performance analysis metrics. Thanks to the advanced capabilities of the Avery VIP, claims Browy, engineers can work more efficiently, develop more complex tests, and work on more complex topologies, such as multi-path, multi-link solutions. The company’s compliance test suites offer effective core -through-chip-level tests, including those used in compliance workshops as well as extended tests developed by Avery to cover the specification features.

The VIP suite adds key CXL 3.0 updates to the 2.0 VIP offering. Some of the additions include:

- Double the bandwidth using PCIe 6.0 PHY for 64 GT/s

- Fabric capabilities

- Multi-headed and fabric-attached devices

- Enhanced fabric management

- Composable disaggregated infrastructure

- Improved capability for better scalability and resource utilization

- Enhanced memory pooling

- Multi-level switching

- Direct memory/ Peer-to-Peer accesses by devices

- New symmetric memory capabilities

Additional capabilities and features included in the VIP CXL 3.0 release include:

- Additional CXL switch agent with fabric manager support

- Support for AMBA® CHI to CXL/PCIe via CXS

- Dynamic configuration of VIP for legacy PCIe, CXL 3.0, 2.0 or CXL 1.1 including CXL device types 1-3

- Realistic traffic arbitration among CXL.IO, CXL.Cache, CXL.Mem and CXL control packets.

- Unified user application data class for both pure PCIe and CXL traffic.

In addition to the CXL 3.0 support mentioned above, Avery has recently announced extensions to its QEMU-CXL virtual platform specifically for the 3.0 version. The enhancements include the latest linux kernel 5.19.8 supporting CXL and interoperability tests such as using ndctl for memory pooling provisioning, resets and Sx states, and Google stressapptest using randomized traffic from processor to HDM, creating realistic high-workload situations.

Co-simulating the SoC RTL with a QEMU open software virtual machine emulator environment rnel allows software engineers to natively develop and build custom firmware, drivers, and applications. They can then run them unaltered as part of a comprehensive system-level validation process using the actual SoC RTL hardware design. In a complementary manner, hardware engineers can evaluate how the SoC performs through executing UEFI and OS boot and custom driver initialization sequences, Additionally, designers can run real application workloads and utilize the CXL protocol aware debugging features of the VIP to effectively investigate any hardware related issues.

“Combined with our CXL compliant VIP, our QEMU CXL virtual platform and VIP co-simulation enables complete CXL system-level bring-up of SoCs in a Linux environment. With this approach customers can address new CXL 3.0 design and verification challenges even when no mainstream commercial platforms support the latest standards,” said Chris Browy, vice president sales/marketing at Avery.

Through the development of VIP, Browy feels that Avery enables system and SOC design teams to achieve dramatic functional verification productivity improvements through the comprehensive VIP and virtual platforms.

Also Read:

Verifying Inter-Chiplet Communication

Data Processing Unit (DPU) uses Verification IP (VIP) for PCI Express

PCIe 6.0, LPDDR5, HBM2E and HBM3 Speed Adapters to FPGA Prototyping Solutions

Share this post via:

From the Selfie to Samantha: The Next Trillion-Dollar Behavior