At the recent TSMC OIP Ecosystem Forum in Santa Clara, there was an important presentation that laid the groundwork for a great deal of future innovation. Alchip and its IP and EDA partner Synopsys presented Efficient 3D Chiplet Stacking Using TSMC SoIC. The concept of 3D, chiplet-based design certainly isn’t new. SemiWiki maintains dedicated forums on both Chiplets and 3D IC. There is a lot of buzz on both topics.

And TSMC’s SoIC initiative provides the manufacturing infrastructure and technical support to achieve next-generation innovation. Indeed, all the elements needed for 3D chiplet-based design are taking shape. It has been said that the devil is in the details. And the details and technical challenges to be overcome as we move to a new chapter in semiconductors are daunting. Meaningful progress to reduce these challenges is quite important, and that progress was on full display at the Alchip presentation. Let’s examine how Alchip is paving the way to future 3D design innovation.

Alchip at TSMC OIP

The presenter from Alchip was Erez Shaizaf, Alchip’s Chief Technical Officer. Erez has been with Alchip for the past two years. He has a long career in semiconductors with companies such as Freescale, EZchip, Mellanox, and Xsight Labs. Erez discussed how Alchip, working with Synopsys and TSMC, has overcome several significant challenges for 3D IC design in the areas of electrical, power, thermal and mechanical design.

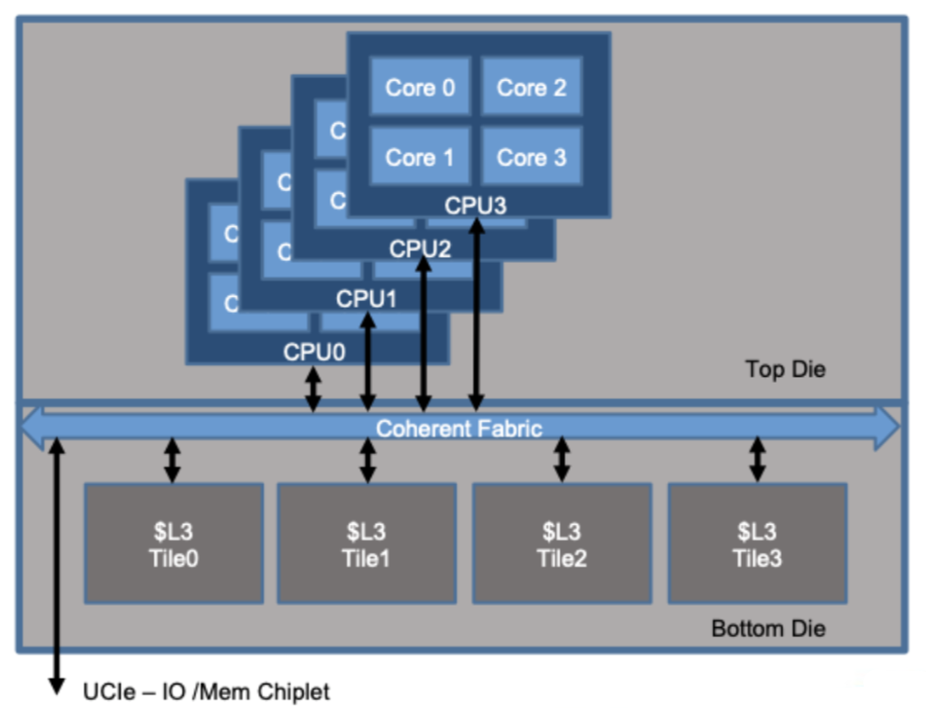

Erez described the kind of 3D architecture being addressed as one that contains top dies in advanced nodes (e.g., high-frequency CPU) and bottom dies in older nodes (e.g., memory subsystems). A coherent fabric connects the two layers with an Alchip Micro 3D liteIO PHY interface. Fine pitch hybrid bonding and fine pitch TSVs create high bandwidth interconnect and efficient power delivery between the top and bottom dies. The figure below illustrates this 3DIC folded CPU use case.

Erez also discussed several power delivery challenges, including:

- Power Integrity Challenges

- Static and dynamic IR drop

- Power noise propagation from bottom to top die and vice versa

- Different power domains among top and bottom dies and a shared ground plane

- Power Grid Design

- TSV distribution

- B distribution

- PDN design

- Power Integrity Simulation and Signoff

- Early analysis (prior to place & route)

- Early simulation (after place & route)

- Signoff

The paper also described a sophisticated TSV distribution strategy that uses non-uniform and location-dependent TSV arrays. Using this approach, TSV density is determined by local power density for bottom and top die shared and non-shared power delivery networks (PDNs). Erez detailed the pros and cons of shared vs. non-shared PDNs. He explained that non-uniform TSV density schemes are friendly to automated place & route. The TSV patterns are compatible with Alchip’s multiple 3D-liteIO micro-PHY P&R and TSMC design rules.

Erez also talked about how to do early PDN analysis and the benefits that result. He also discussed how to achieve 3D data and clock design targets and details of an H-tree strategy for 3DIC clocking. 3DIC thermal characterization challenges and solutions were also presented, along with a set of verification strategies aimed at 3DIC design.

Abhijeet Chakraborty, Vice President Engineering at Synopsys, followed Erez to the podium. Abhijeet has been with Synopsys more than 18 years. He described how the Synopsys 3DIC Compiler delivers a unified exploration-to-signoff platform. The benefits of this platform include:

- Extending 2D fusion platform (Fusion Compiler) for 3D heterogenous integration (3DHI) and advanced packaging

- Delivering a unified environment that supports 3D design exploration, planning, implementation and verification

- Integrating the golden signoff solutions from Synopsys and Ansys for 3D STA, EM/IR, SI/PI/TI, EMAG

- Providing full support for TSMC technologies including CoWoS, SOIC, and 3Dblox

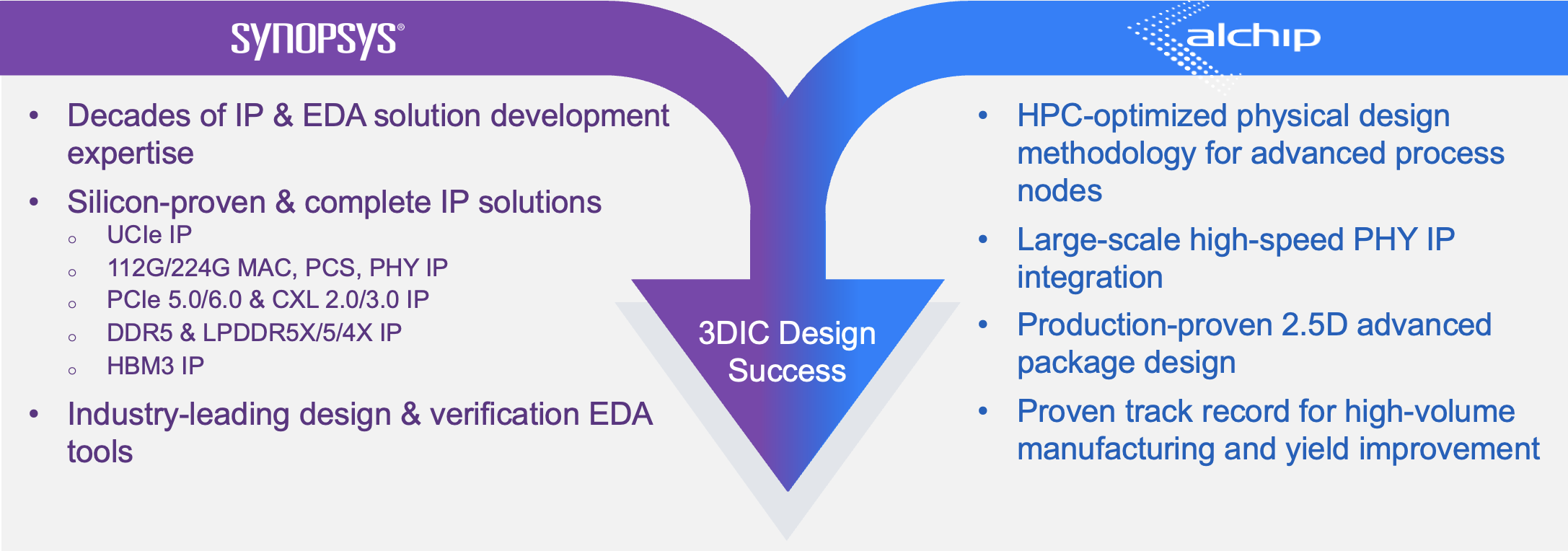

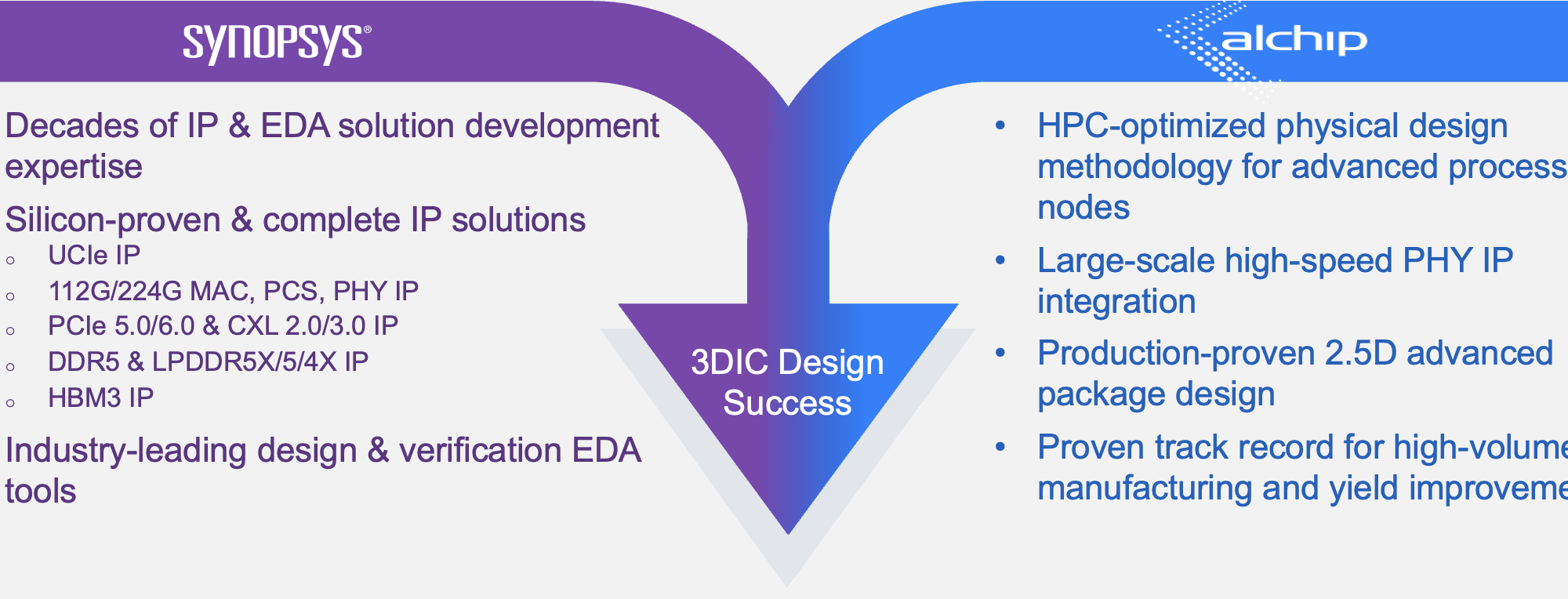

Overall, Abhijeet explained that Synopsys and Alchip are collaborating on HPC/AI-optimized physical design for advanced nodes, IP and multi-die packaging. The graphic at the top of this post provides a high-level summary of how Synopsys and Alchip are enabling 3DIC design success.

The Implications of This Work

I had a chance to speak with Erez Shaizaf after the presentation. He gave me some perspective on the implications of the work presented. In a word, it’s transformative.

Erez explained that up to now, most multi-die designs consisted of active devices, like AI accelerators and some HBM memory stacks over passive devices, like caps and interconnect supplied by the interposer. The work presented at OIP opens the possibility for multiple active devices in the stack to come from different technology nodes. He predicted these new options will change the designer’s mindset and system design will take on new meaning.

He explained that the ability to integrate multiple active devices in a true 3D stack with multiple process nodes opens many new options for system architecture and integration. One benefit of this approach is partitioning a subsystem from one large die to multiple smaller dies. This delivers a yield and cost benefit. There are many more examples of how a more unconstrained 3D design flow can change the game.

He pointed out that the yield, thermal, mechanical and power delivery aspects of true multi-dimensional system design are substantial. The way design will be done will change as well. But the opportunities for true system innovation make it all worthwhile.

Erez concluded by saying that Alchip and Synopsys are breaking down the barriers to this new design paradigm. Along with TSMC, they are bringing new opportunities for innovation within reach, and that makes for an exciting future.

To Learn More

You can find out more about the TSMC Global OIP Ecosystem Forum here. If you are considering the benefits of 3DIC design, you will want to learn more about how Alchip can help. You can access more information about Alchip here. Even better, you can reach out to the company to discuss your future design needs here. And that’s how Alchip is paving the way to future 3D design innovation.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.