Synopsys announced on October 24 new DesignWare[SUP]®[/SUP] Memory Interface IP solutions supporting the next-generation DDR5 and LPDDR5 SDRAMs. The DDR5 and LPDDR5 IP significantly increase memory interface bandwidth compared to DDR4 and LPDDR4/4X SDRAM interfaces, while reducing area and improving power efficiency. The DesignWare DDR5 IP, operating at up to 4800 Mbps data rates, can interface with multiple DIMMs per channel up to 80 bits wide, delivering the fastest DDR memory interface solution for artificial intelligence (AI) and data center system-on-chips (SoCs).

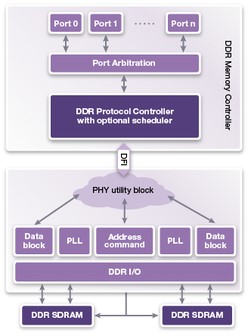

The industry’s first LPDDR5 IP, running at up to 6400 Mbps, provides significant area and power savings for mobile and automotive SoCs with its dual-channel memory interface option that shares common circuitry between independent channels. For additional power savings, the DesignWare Memory Interface IP solutions provide several low-power states with short exit latencies and offer multiple pre-trained states for dynamic frequency change capability. The DDR5 and LPDDR5 controller and PHY seamlessly interoperate via the latest DFI 5.0 interface, providing a complete memory interface IP solution for high-bandwidth, low-power SoC designs.

DesignWare DDR IP Solutions

[table] border=”1″ cellspacing=”0″ cellpadding=”0″ style=”width: 100%”

|-

| style=”width: 15.32%” | DesignWare DDR PHY(New)

(full list here)

| style=”width: 33.92%” | SDRAMs Supported /

Maximum Data Rate

| style=”width: 15.9%” | Interface to Memory

Controller

| style=”width: 34.86%” | Typical Application

|-

| style=”width: 15.32%” | LPDDR5/4/4X

| style=”width: 33.92%” | LPDDR5 / 6400 Mbps

LPDDR4 / 4267 Mbps

LPDDR4X/ 4267 Mbps

| style=”width: 15.9%” | DFI 5.0

| style=”width: 34.86%” | Design in 16-nm and below that requires high-performance mobile SDRAM support up to 6400 Mbps

|-

| style=”width: 15.32%” | DDR5/4

| style=”width: 33.92%” | DDR5 / 4800 Mbps

DDR4 / 3200 Mbps

| style=”width: 15.9%” | DFI 5.0

| style=”width: 34.86%” | Design in 16-nm and below that requires high-performance DDR5/4 support up to 4800 Mbps

|-

Some highlights:

- The industry’s first LPDDR5 controller, PHY, verification, and IP solution support data rates up to 6400 Mbps with up to 40% less area than previous generations

- The complete DDR5 IP solution supports up to 4800 Mbps with single, dual channels for discrete devices and DIMMs

- Both solutions provide several low-power states with short exit latencies and offer multiple pre-trained states for dynamic frequency change capability

The DesignWare DDR5 and LPDDR5 IP solutions support all required features of the DDR and LPDDR specifications, enabling designers to incorporate the necessary functionality into their SoCs:

- Firmware-based training via an embedded calibration processor in the PHY optimizes the boot-time memory training for highest data reliability and margin at the system level. It also allows fast updates to the training algorithms without requiring changes to the hardware

- Decision feedback equalization (DFE) used in the input receivers reduces the impact of inter-symbol interference (ISI) to improve signal integrity

- Reliability, availability, serviceability (RAS) features, including inline or sideband error correcting code (ECC), parity, and data cyclic redundancy checks (CRC), reduce system downtime

- Synopsys PHY hardening and signal/power integrity expertise enable faster design completion time and a higher design confidence degree.

- Synopsys VIP for DDR5 and LPDDR5 provides randomized configuration and runtime selection, as well as built-in comprehensive coverage, verification plan, and protocol checks for increased productivity.

ARM, Micron and SK Hynix provided testimonials in a Synopsys press release on October 24, 2018. In that press release John Koeter, vice president of Marketing for IP at Synopsys, emphasized that Emerging applications such as AI, automotive, and cloud are requiring significantly higher memory bandwidth to address the massive amount of data throughput. He added that Synopsys is offering designers the fastest DDR5 and LPDDR5 IP solutions on the most advanced FinFET processes to deliver innovative products that are differentiated in bandwidth, power, and area.

Availability

- The DesignWare DDR5 PHY and LPDDR5 PHY are scheduled to be available in Q1 of 2019

- The DesignWare DDR5 Controller and LPDDR5 Controller are scheduled to be available in Q2 of 2019

- The VC Verification IP for DDR5 and LPDDR5 is available now.

Worth Noting

- All the DFI-compatible DDR PHYs are supported by Synopsys’ unique DesignWare DDR PHY Compiler. In addition, Synopsys’ DesignWare DDR5/4 Controller, LPDDR5/4/4X Controller, and Enhanced Universal DDR Memory and Protocol Controller IP feature a DFI-compliant interface, low latency and low gate count while offering high bandwidth. Optional market-specific features like AMBA AXI/4 AXI Quality of Service (QoS) and Reliability, Availability, and Serviceability (RAS) features allow you to match the area and capabilities of the controllers to designer needs.

- Synopsys also offers DesignWare HBM2 IP, which provides 12x the bandwidth of DDR4 IP and ten times better power efficiency for graphics, high-performance computing, and networking SoCs.

DesignWare[SUP]®[/SUP] Memory Interface IP solutions

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.