Synopsys hosted a tutorial on verification for low power design at DVCon this year, including speakers from Samsung, Broadcom, Intel and Synopsys. Verification for low power is a complex and many-faceted topic so this was a very useful update. There is a vast abundance of information in the slides which I can’t hope to summarize in a short blog so I’ll just highlight a few points that stood out for me. I suggest you get your hands on the slides (Tutorial 6 from the DVCon 2017 set) for more detailed study.

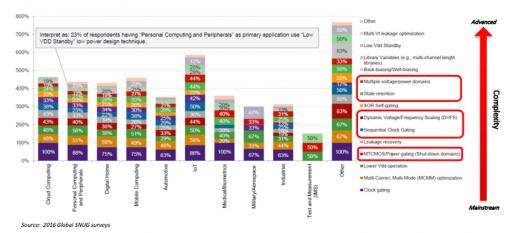

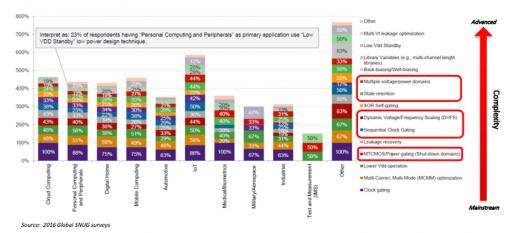

The tutorial kicked off with a review (by Amol Herlekar of Synopsys) on trends in low-power design based on global SNUG 2016 surveys. One surprising observation is just how many advanced power saving techniques are being used across a wide variety of applications, from cloud computing to PCs, digital home, mobile, auto, IoT, medical, mil-aero, industrial and test and measurement. I remember when, not so long ago, many designers thought the world of power management was bounded by clock gating, but now the survey shows widespread adoption of power gating, sequential clock gating, DVFS (wow!), state retention and use of multiple power and voltage domains. The bulk of respondents were using 10 or less voltage domains and 10 or less power domains, but that’s still a lot.

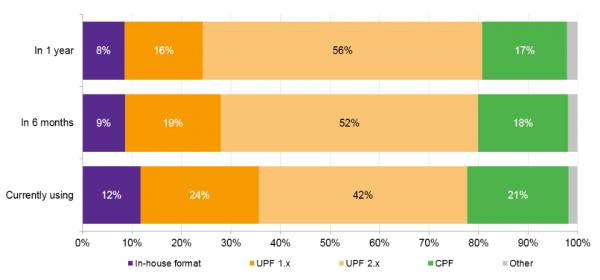

Users continue to migrate to UPF (>70% within a year) and especially UPF 2.0, while other formats continue to lose mindshare. And while UPF has made an impossible task possible, there are still many questions around best methodologies – how to deal with analog and other hard IP, how best to organize LP verification, how to get good coverage of low power states and transitions and how best to verify a PG netlist (remember all those switches for power and voltage gating?) Follow-on tutorials provided advice for verification engineers in the trenches on how they approach these problems.

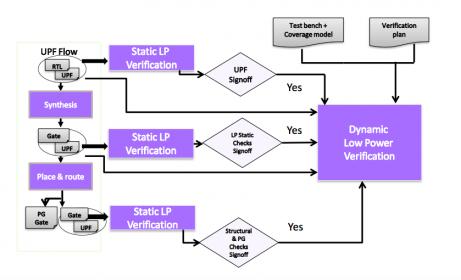

Amol also presented the Synopsys top-level recommendation for a power verification flow – always get static verification clean, then proceed to dynamic verification and do this at RTL, post-synthesis and post-layout. Other speakers largely echoed these points (with a lot more elaboration on details), starting with Vikas Gupta from Samsung, who provided guidelines specifically on static verification. He talked about hierarchical UPF verification and the care required in getting this right, such as managing multiple instances of a block potentially appearing in different power configurations. He also stressed the importance of fully validating the UPF at each stage (RTL, post-synthesis, post implementation). And he stressed that in their environment, waivers are not allowed; you must get the UPF clean the right way, not by fudging.

One of my take-aways from this section was that static verification is manageable if (and possibly only if) you follow a disciplined approach to constructing and checking the UPF at each stage. My other take-away was that effectively what we have today solves half of the power intent problem; from UPF we can verify power intent, but the assembly of that intent is still (for most) largely manual. Users need tools/templates that will help build UPF following best practice guidelines for assembly closer to correct by construction.

Broadcom followed with a discussion on verification challenges. This presentation was from YC Wong; if anyone can stress-test an EDA concept or tool, YC and his team will get there first, so I’m unsurprised that he got this piece of the tutorial. Incidentally, he called out VC LP, VCS-NLP and Verdi use in their flow. For YC, it’s ultimately it’s all about PG netlist validation. Not the way many of us think about it but you can’t fault the reasoning. The PG netlist contains all the power and voltage switches and other power connections which are only implied (through UPF) in earlier gate/RTL representations. So his team starts by building a PG netlist (mapped, no optimization) even before they hand off to synthesis, and they run static verification on that netlist. And of course, they repeat this on the LVS netlist before checking LP strategies.

He also re-emphasized that you should do everything (at each stage) to maximize static verification before you get into dynamic verification. Static in this context isn’t just UPF linting versus RTL/gate netlists. It also includes formal and X-prop analysis. Especially when you get to PG simulation, it is way too expensive to be finding problems that could have been found statically. He particularly stressed the value of X-prop analysis in finding potential sequencing issues before you get into dynamic verification.

Satya Ayyagari from Intel closed with a discussion on low power simulation (where they use VCS-NLP and X-prop). Satya gave a very detailed description of strategies to approach different kinds of IP and to approach full-chip LP simulation, both on a simulator and in emulation (and even prototyping). Attention to gate level simulation was interesting, for mission mode, for power sequencing and for scan testing where scan paths cross power domains. Emulation was stressed as important for full-chip power verification across use cases, but he mentioned a point I didn’t realize – that he has seen no good method to handle power state tables in emulation. Satya suggested as a closing point that LP modeling would benefit for some level of understanding of voltage in logic verification; not the AMS kind of understanding which would be too slow, but enough to trap potential mismatches in level shifter and voltage switching expectations.

Srinivasan Venkataramanan in the audience asked a bunch of questions. I learned afterwards that he works at a verification consulting group in Bangalore. He liked a topic on complex power switches, raised by YC (which will require further extensions to UPF). He also liked the detail (in the trenches he called it), especially from the Intel speaker. And he liked that Synopsys acknowledged the need for extended assertion capabilities beyond standard SVA. Overall he said he really found high value in this tutorial, a notable endorsement from an independent member of the audience.

You can find the slides HERE. To get these you will need to have registered as a participant and you will need your badge ID from the event. Or you can just talk to a colleague who already downloaded the slides 😎.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.