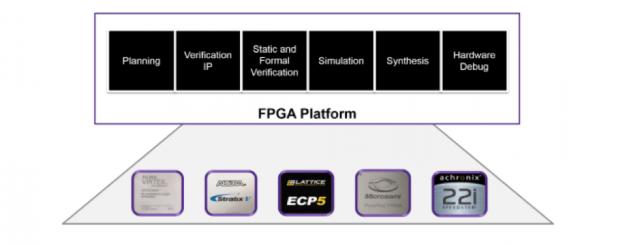

I am sure there are many FPGA designers who are quite content to rely on hardware vendor tools to define, check, implement and burn their FPGAs, and who prefer to test in-system to validate functionality. But that approach is unlikely to work when you’re building on the big SoC platforms – Zynq, Arria and even the big non-SoC devices.… Read More

Tag: static

Recipes for Low Power Verification

Synopsys hosted a tutorial on verification for low power design at DVCon this year, including speakers from Samsung, Broadcom, Intel and Synopsys. Verification for low power is a complex and many-faceted topic so this was a very useful update. There is a vast abundance of information in the slides which I can’t hope to summarize… Read More

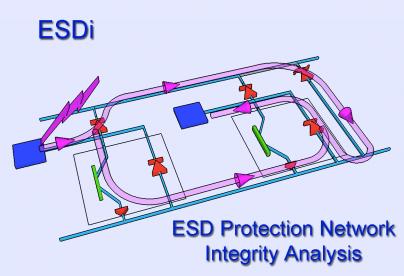

ESD Protection Network Checking is Difficult But Necessary

I’ve written before about anti-fuse non-volatile memory, where the gate oxide is intentionally damaged in order to create a readable bit of data, but this is what most circuit designers never want to have happen to their logic gates. However, since the advent of MOS transistors the issue of Electrostatic Discharge (ESD) and the… Read More

Synopsys Revamps Formal at #51DAC

Synopsys announced verification compiler a couple of months ago and dropped hints about their static and formal verification. They haven’t announced anything much for a couple of years and it turns out that the reason was that they decided that the technology that they had, some internally developed and some acquired, … Read More