Synopsys have been gradually broadening their portfolio of verification IP (VIP). It is 100% native SystemVerilog with native debug using Verdi (that was acquired from SpringSoft last year, now fully integrated into Verification Compiler). It has native performance with VCS. Going forward there are source code test suites.

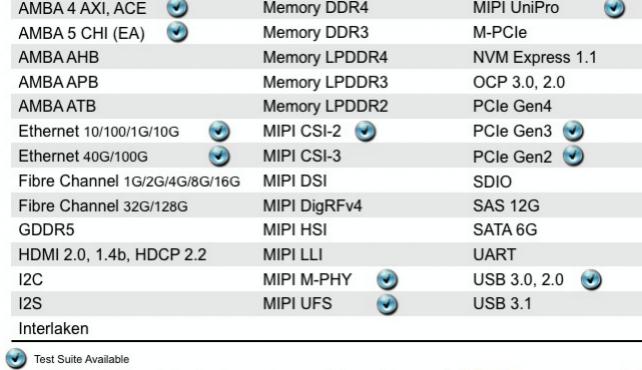

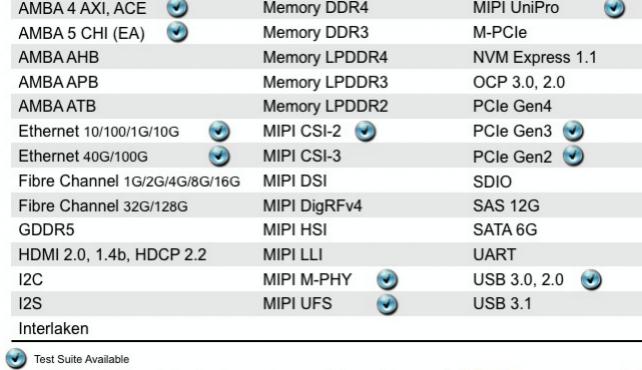

Most of Synopsys IP has been focused on buses and interfaces such as AMBA, PCI, ethernet and so on. See the table below. In a major change they have a growing portfolio of VIP for memories. This is a market that has historically been dominated by another company (famous for parties at DAC in case you need a hint).

As Synopsys pulls all their verification together in a much more seamless environment under the name Verification Compiler, making everything run seamlessly together has become increasingly important. The initial focus has been on DDR3/4 and LPDDR2/3/4. They are not making any more announcements at the moment but for sure they are working on continuing to broaden the portfolio to cover things like flash.

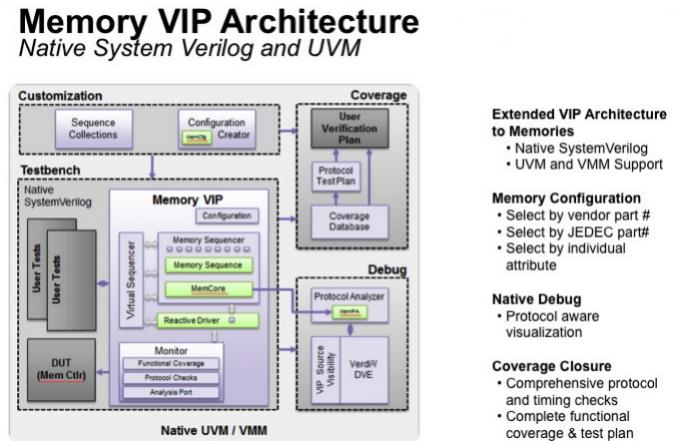

The picture above shows how all the moving parts go together. The primary differentiators of the Synopsys approach are:

- Based on proven SystemVerilog VIP technology and base class library

- Simplified use-model and ease-of-use for UVM testbenches

- Strong foundation of proven base classes

- Integrated with Protocol Analyzer

- Configures to Specific Components

- Vendor memories

- Includes DIMM, RDIMM, LRDIMM, UDIMM

- DIMM logic + buffers

- Validated against internal SNPS memory controllers and customer designs

The memory VIP has the features you would expect such as being able to bypass memory initialization to reduce simulation time, direct access to the memory to examine or alter contents, error injection and exception testing, skew injection, protocol and timing check. The functional coverage is fully integrated into the VIP and protocol verification plan.

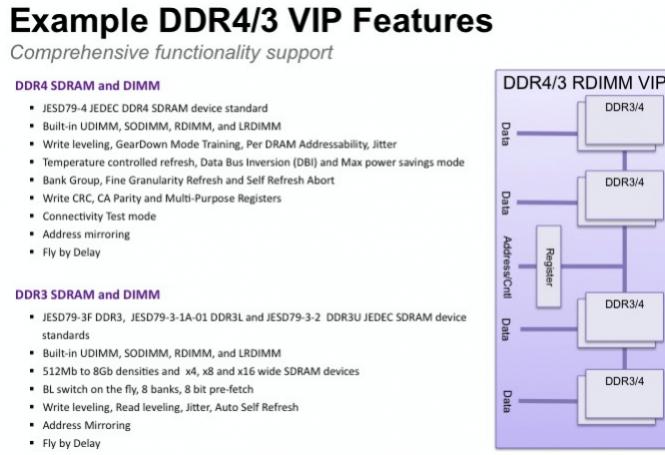

As an example, here are the DDR3/4 VIP features. Not being a in-depth memory expert there are one or two things that I am not sure what they are, such as fly by delay. It think it is the tuning needed at these high speeds but it also sounds like being 8th in line for takeoff at SFO.

More details on all Synopsys VIP is here, including datasheets for the memory VIP.

More articles by Paul McLellan…

Comments

There are no comments yet.

You must register or log in to view/post comments.