Despite sounding like a minor enhancement version for USB, USB 3.2 introduces many important changes for the USB specification. To see where USB has come from and where it is going, it is essential to look at what is found in USB 3.2. The other salient point is that now the Type-C connector has split out from the underlying USB specification and takes on a life of its own. Additionally, it is important to understand USB 3.2 because it plays a key role in the USB4 standard.

Synopsys, as a major provider of USB IP and contributor to the standards, has published an informative white paper that clearly explains what is new in the USB 3.2 specification and how all the elements, including the Type-C connector work together. The paper written by Morten Christiansen, Technical Marketing Manager at Synopsys, is titled “USB 3.2: A USB Type-C Challenge for SoC Designers”.

USB 3.0 was fine for mechanical disk drives with spinning platters, but Flash based SSD drives easily exceed the available bandwidth. USB 3.2 offers up to 20Gbps, which is four times the throughput of USB 3.0. USB 3.2 also allows more flexibility for connected display devices. In addition to adding support for longer cables for video, it also allows for an alternate mode for higher bandwidth video using all of its additional lanes to carry display data.

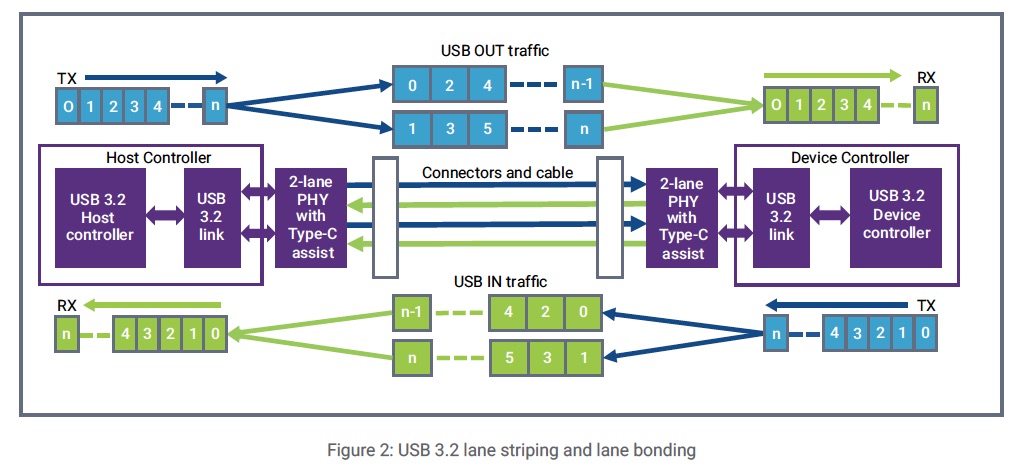

This brings us to why Type-C connectors are so important to USB 3.2 and beyond. There are four sets of differential pairs on the Type-C connector. Previously with 3.1 and 3.0 only one TX and RX pair was used. The actual pairs used depended on the orientation of the connector. The nomenclature for USB 3.2 connections speeds is noted as Gen X x Y, where X denotes the lane speed and the Y denotes the number of lanes used. Gen 1 is 5Gbps, and Gen 2 is 10 Gbps. Thus, Gen 2×1 is one lane at 10G and Gen 1×2 is 2 lanes at 5G each for a total of 10G. Consumer facing information on speeds will focus on the resultant speed and not on the internal mechanics or version numbers.

Higher data rates open up some interesting options for using USB in new ways. Synopsys suggests that using existing USB ports for debug data can save on extra hardware ports and allow for much better tracing and debug. Synopsys USB device controllers support External Buffer Control (EBC) for efficient movement of debug data through USB ports. The automotive market will also see benefits from USB 3.2 due to longer permitted cable lengths. Higher data rates here will also help speed infotainment system firmware and application updates. These might include maps and navigation data, etc.

The Synopsys white paper does an excellent job of describing the lane bonding and data striping that is used to increase transfer rates. The paper also talks about the changes required to the USB controller to handle the Ordered Sets for USB 3.2 and the encoding it uses. They point out that the higher 20 Gbps data rates can reveal issues in existing device controller CPU/memory configurations or software stacks, even though the previous software stack is compatible with USB 3.2. In the PHY it is essential to move to two independent RX/TX lane pairs and a digital crossbar instead of relying on analog multiplexers, as was sufficient with the older Gen 1 data rates.

At the end of the paper the author discusses the methods that Synopsys uses to prototype and test their IP and silicon. They use HAPS-80 FPGA based prototyping systems for their USB 3.2 IP controller development. For example, they are able to set up systems with both prototyped USB 3.2 Hosts and Device controllers. With this they can run the xHCI software stack on a connected Windows system.

Synopsys includes links to USB 3.2 resources for those interested in digging deeper. Their paper does a good job of spelling out the important points needed to better understand USB 3.2 and how it fits into the entire USB roadmap. As mentioned before, they touch on how USB 3.2 fits into USB4 and will continue to play an important role as USB moves forward. The paper is available for download at the Synopsys website.

Also Read:

Synopsys is Enabling the Cloud Computing Revolution

Synopsys Delivers a Brief History of AI chips and Specialty AI IP

The Heart of Trust in the Cloud. Hardware Security IP

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.