We have already discussed the recently released M-PCIe ECN from PCI-SIG in Semiwiki at the end of 2012, but the new “standard” (in fact an Engineering Change from PCI-SIG and MIPI Alliance) was only real on paper, at that time. The upcoming webinar from Synopsys, M-PCIe: Utilizing Low-Power PCI Express in Mobile Designs, shows that the concept is turning into a real IP product. This pretty fast response time (between six months and one year) is justified by two reasons. At first, both PCIe Controller IP and MIPI M-PHY IP are already available in Synopsys IP port-folio, the challenge was to integrate both IP together and validate it, a faster task than developing from scratch.

The second reason, in my opinion, is that many chip maker and OEM were expecting to be able to use PCI Express protocol in the mobile (smartphone and media tablet) segments. I suspect that many of the previously active actors in the PC segment, discovering that the market was moving to every kind of mobile systems, have decided to follow the market, and also move to mobile. This means designing for low power, and MIPI M-PHY is known to exhibit a far better power efficiency that PCIe PHY. Then, adopting M-PCIe is a good way to preserve a 10 years investment into PCI Express related development, hardware, drivers and software, and to attack a new segment with good technical arguments…

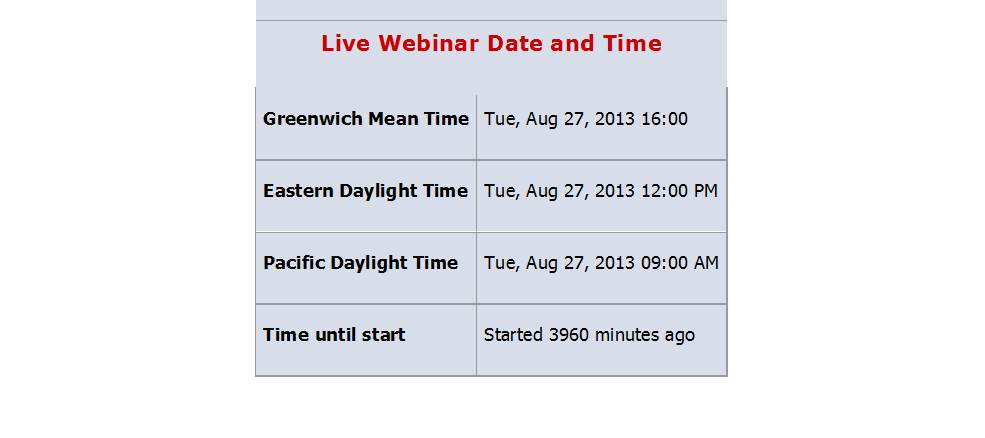

If you are interested to listen to the webinar “live”, you should rush, at this webinar will be held today! Tuesday, the 27[SUP]th[/SUP]…

Last point, as you can see below, one of the presenter is Richard Solomon, who has served in the board of Directors of the PCI-SIG for almost 10 years, he is probably one of the best knowledgeable person about PCI Express!

You can Register here

Designers utilizing PCI Express are looking to lower the power of their designs by incorporating the M-PCIe ECN from PCI-SIG. The recently released M-PCIe ECN adapts the PCI Express protocol for use with the MIPI M-PHY, benefiting applications that require low-power usage such as mobile products. To incorporate PCI Express with the M-PHY, device designers should understand the top issues they’ll need to consider.

This advanced technical webinar will begin with a quick overview of the specification and its application space, and then go into details such as bandwidth and clocking considerations, PHY interface differences, power management impacts, and the tradeoffs related to choices around link-layer changes. These changes may impact the transaction and application layers of devices moving from PCIe to M-PCIe, and the webinar will detail those issues. A basic understanding of PCI Express concepts is helpful.

Attendees will learn:

- M-PCIe bandwidth and clocking considerations

- M-PCIe power management

- The tradeoffs related to the link-layer changes

- PHY interface, transaction layer, and application layer differences between PCIe and M-PCIe

Who should attend:

- System architects

- PCI Express device designers

- Mobile device designers

Presenters:

Scott Knowlton, Product Marketing Manager, Sr. Staff, DesignWare PCI Express, PCI-X, PCI and SATA IP, Synopsys

Scott Knowlton joined Synopsys in 1997 and has extensive experience in PCI Express, SATA, and AMBA IP as well as Synopsys’ coreTools product lines. Prior to joining Synopsys, Scott worked in simulation, synthesis and mixed signal solutions at Cadence Design Systems after several engineering and project management positions in ASIC development at Encore Computer, Intrinsix, and Raytheon. Scott earned his Bachelor of Science degree in Electrical Engineering from the University of Michigan.

Richard Solomon, Technical Marketing Manager, DesignWare PCI Express Controller IP, Synopsys

Richard Solomon has been involved in the development of PCI chips dating back to the NCR 53C810 and pre-1.0 versions of the PCI spec. Prior to joining Synopsys, Richard architected and led the development of the PCI Express and PCI-X interface cores used in LSI’s line of storage RAID controller chips. He has served on the PCI-SIG Board of Directors for over 10 years, and is currently Vice-President of the PCI-SIG. Richard holds a BSEE from Rice University and 25 US Patents, many of which relate to PCI technology.

Eric Esteve from IPNEST

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.