TSMC attends DAC every year and they do something very savvy, it’s a theatre where they invite all of their EDA and IP partners to present something of interest, followed by a drawing for a prize. At the end of the day they even have a nice prize, like a MacBook Air, which I didn’t win. On Wednesday I watched Dave Reed of Synopsys present an update on the Custom Design Platform.

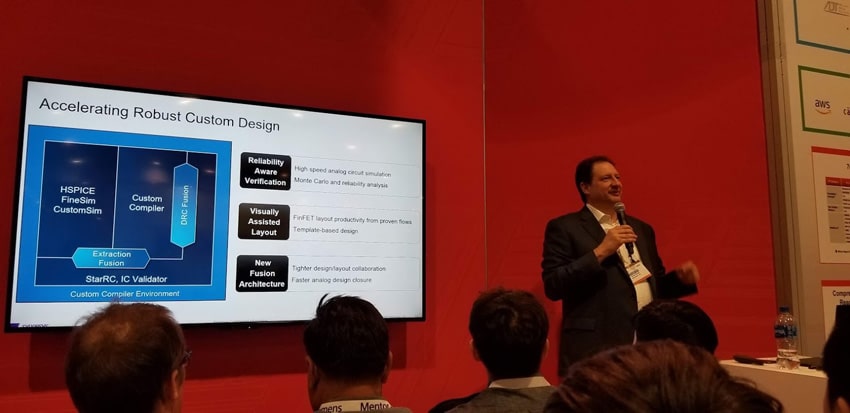

Tools in the Custom Design Platform include:

- Circuit Simulation (HSPICE, FineSim, CustomSim)

- IC Layout Editor (Custom Compiler)

- RC Extraction (StarRC)

- DRC/LVS (IC Validator)

Back in April they announced that these tools were certified by TSMC for the 5nm FinFET process node, which is always a big deal for IC design teams pushing the bleeding edge because you need your EDA tools ready.

The integration between these tools is tight, so the phrase used is DRC Fusion or Extraction Fusion, because users don’t want to wait hours streaming data out of one tool and made compatible with the next tool in the flow. Adoption of the Custom Compiler tool increased this past year, now with 100 logos and 3,000 users, and all internal Synopsys IP designs use their own tools.

Analog IC designers know that layout parasitics will affect the performance, accuracy and reliability of their circuits, so the Synopsys flow allows for early use of parasitic estimates, followed by partial extraction and fully extracted netlists.

Each new, smaller process node has an increase in circuit simulations and increase in parasitics, so FineSim can be used to simulate circuits like SERDES, PLL and ADC, now about 3X faster than before. Plus, they’ve added RF simulation to FineSim, so you have another choice than HSPICE.

Automating the layout of analog design is a noble quest, tried by many vendors in the past, so Synopsys continues with a template-based approach where expert layout designers capture their best practices, allowing for transistor size changes. All this is done without having to write code, or becoming a computer science major. I asked Dave about the CiraNova technology that they acquired years ago, and it’s still be used under the hood for layout automation.

IC designers used to work in either a digital or an analog environment, with tedious file interchanges between them, but not any more because Synopsys allows seamless use between the digital flow of IC Compiler II and the analog flow of Custom Compiler. DRC checking can be done either in batch mode or even interactively, saving you time.

Summary

If the Custom Design Platform can be used internally at Synopsys for creating all of their own IP in TSMC nodes at 28nm all the way down to 5nm, then it’s going to work for your project too. This is a competitive market segment and Synopsys keeps plugging away, year by year, making it easier to reach design closure through clever automation.

Related Blogs

- Physical Verification with IC Validator

- AMS Experts Share IC Design Stories at #55DAC

- Daniel’s #55DAC Trip Report

Comments

There are no comments yet.

You must register or log in to view/post comments.