One year ago I met with Hany Elhak of Synopsys to get an update on what was new with HSPICE in 2011, so this year at DAC Hany met me at the Synopsys booth for a quick update.

HSPICE has something called Precision Parallel so with 16 cores your IC circuit simulations will have about 10 x speed up compared to a single core.

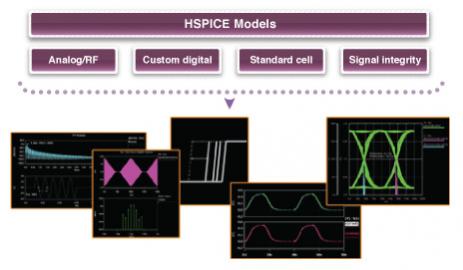

There’s a new FinFET model from UC Berkeley called BSIM-CMG that is now supported in HSPICE.

About the actual SPICE product roadmap (FineSim SPICE, FineSim PRO, HSPICE, XA, HSIM) please see your Synopsys sales rep to setup a meeting.

There is now support for 3D IC design where you can run a single netlist using modules of different libraries, so each IC will have it’s own PVT specified instead of using a single PVT corner.

The syntax of HSPICE has been extended to allow multi-chip and 3D or interposer simulations.

Device aging in HSPICE is now qualified for 28nm and 20nm processes.

There’s a new algorithm for S-parameters (HDMI cables, backplanes for 10G) with long delay systems (transient is 60x faster and long bit streams).

Summary

I’m sure that Synopsys is quite glad to have FineSim Spice in their product portfolio now instead of competing against it with HSPICE. My guess is that FineSim Spice continues to live on and probably gets merged with HSPICE since they basically serve the identical IC designers. Who knows, maybe HSPICE will get a new switch, something like -finesim to simulate with the FineSim SPICE algorithm.

FineSim even made it into the list of tools for DAC by Synopsys.

The SPICE circuit simulation market place continues to be crowded and competitive (Cadence Spectre, Mentor Eldo, Berkeley DA Analog FastSPICE, etc.). See the full list of SPICE and Fast SPICE vendors on this wiki page.

Share this post via:

Comments

3 Replies to “What’s new with HSPICE at DAC?”

You must register or log in to view/post comments.