As IC designs become increasingly complex, traditional Design Rule Checking (DRC) methods are struggling to keep up. The old “construct by correction” approach, initially developed for simpler, custom layouts, is creating substantial runtime and resource bottlenecks. Traditional DRC relies on an iterative, sequential approach that is not well-suited for today’s automated and multi-layered design hierarchies. New methodologies, such as the “shift-left” approach, are helping to address these challenges. This blog post will explore how Siemens’ Calibre nmDRC Recon, has enabled a shift-left strategy, that allows for faster DRC, maximum check coverage, and minimal hardware usage.

Traditional DRC

Traditional DRC methods involve a manual process where layout designers create shapes, identify violations, and make corrections. While this worked well for simpler designs at larger process nodes, it’s not efficient for today’s automated design environments and smaller process nodes. In modern designs, components are routed individually, and then again at the top-level, plus the final design is assembled at different stages of readiness. Design teams typically run all design rules on all available layouts and then review individual results one-by-one, adjusting as needed. This iterative process can be extremely time-consuming, especially with the complexity of today’s advanced process design rules. Designs are often made up of multiple IP blocks designed by different teams on different timelines, which makes it difficult to have a fully assembled design for full verification. This leads to longer runtimes and higher compute requirements.

Shift-Left Approach

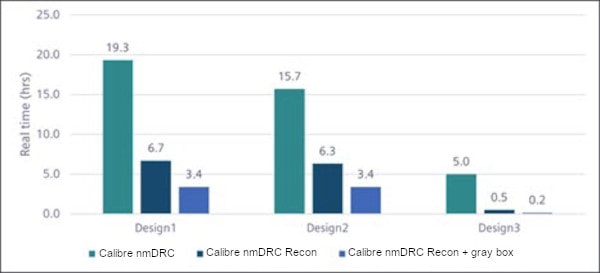

A better approach is to shift verification steps to earlier stages of the design process, significantly reducing debug time and expediting time to tape-out. Calibre nmDRC Recon is designed for early layout, whether at the IP, block, or chip level. It uses AI techniques to identify and run only those rules that are local in scope, meaning those that do not require checking across long distances or hierarchy. By focusing on local checks, Calibre nmDRC Recon significantly reduces runtime and hardware requirements.

The checks are local, so the root-cause of errors are usually close to where the errors are reported. This allows designers to quickly identify and fix system layout issues like floorplan, cell placement, or chip finishing errors. Calibre nmDRC Recon also allows designers to enable or disable certain rules or specify layers that have been changed to automatically enable all dependent rules. Identifying and fixing root-cause problems early on eliminates many individual DRC errors, further reducing the debug time.

Running a subset of checks might seem counterintuitive, but it can reduce overall iteration time. The reason is that gross root-cause problems can be fixed quickly based on local checks. Rules requiring a more global scope, such as those that depend on connectivity information, can be addressed later. For these more global rules, Calibre nmLVS can help by identifying shorts early, ensuring that subsequent DRC iterations are more effective.

Full DRC checking is still necessary for final tape-out, however using techniques like split-deck runs, where checks that require significant runtime or hardware are run in parallel, overall performance can be improved. Using Calibre interactive, the individual results from each split can be combined into a single DRC results database.

Incomplete Designs

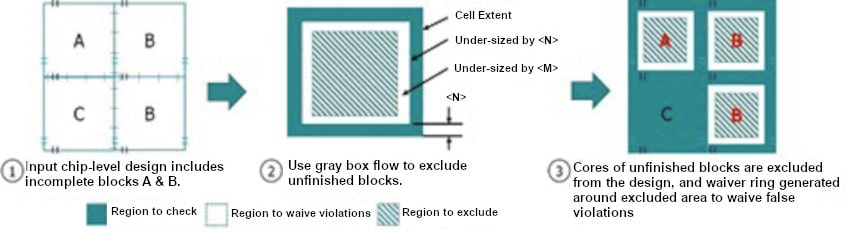

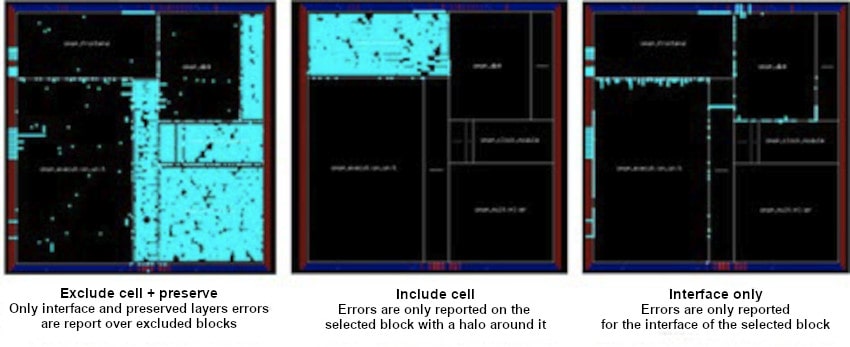

Another challenge is dealing with incomplete designs, as IP blocks of a design are not always ready at the same time. Using a combination of Calibre nmDRC Recon and Calibre nmDRC auto-waivers feature can be used. This allows designers to identify incomplete regions and exclude them from checking using markers. This “gray-boxing” technique allows designers to focus on their specific components of interest while still considering only the context of interest from clean layouts. By eliminating geometries, there is the risk of creating false errors, but the auto-waiver feature allows those errors to be removed so designers can focus on their specific component without impacting other areas of the design.

Combining Recon and auto-waivers has proven to be significantly faster than traditional methods for design layout generation and final tape-out.

Microsoft

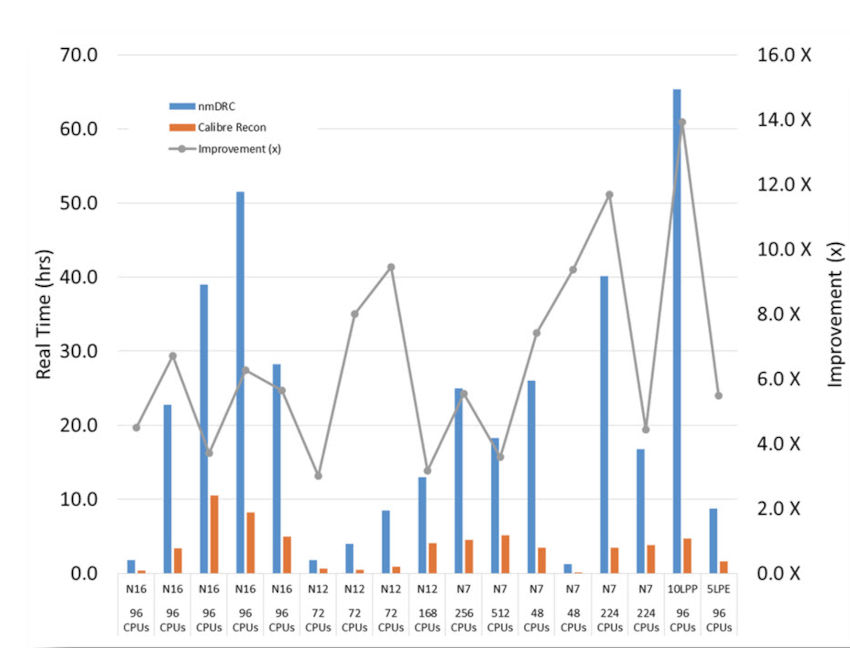

Microsoft used Calibre nmDRC Recon to accelerate their DRC process, achieve maximum check coverage, and minimize hardware use. They started using Calibre nmDRC Recon iterations at the floorplan stage and then at the physical implementation stage. By that point, most of the designs were clean of PG shorts.

Microsoft found that DRC Recon improved their early design stages, as it provided a solid foundation for pinpointing violations efficiently and significantly reduced runtimes. By adopting the shift-left approach with Calibre nmDRC Recon and auto-waivers, Microsoft was able to significantly reduce runtime, hardware requirements, and debugging time.

Conclusion

The shift-left verification strategy, using tools like Calibre nmDRC Recon is critical for addressing the challenges of complex IC designs. By focusing on local checks early, using techniques like auto-waivers, and leveraging split-deck runs, design teams can achieve faster and more efficient IC design. Microsoft showed the benefits of this approach, emphasizing the importance of adopting shift-left verification for achieving faster time-to-market.

Read the 10 page paper online.

Related Blogs

- What are Cloud Flight Plans? Cost-effective use of cloud resources for leading-edge semiconductor design

- Getting the most out of a shift-left IC physical verification flow with the Calibre nmPlatform

- 3DIC Physical Verification, Siemens EDA and TSMC

- DAC 2021 – Siemens EDA talks about using the Cloud

Comments

There are no comments yet.

You must register or log in to view/post comments.