I’ve known about DRC (Design Rule Checking) for IC design, and the same approach can also be applied to PCB design. The continuous evolution of electronics has led to increasingly intricate PCB designs that require Electrical Rule Checking (ERC) to ensure that performance goals are met. This complexity poses several challenges in design verification, often resulting in errors, inefficiencies, and increased costs. This blog post examines these challenges and introduces HyperLynx DRC, an EDA tool from Siemens, to address them.

Modern electronic products demand enhanced functionality and performance, directly impacting the complexity of PCB design and verification. The use of complex components, high-speed interfaces, and advanced materials requires thorough PCB checks to guarantee optimal performance and reliability. This level of complexity often stretches the capabilities of traditional verification methods.

Several factors contribute to the challenges in PCB design and verification:

- Error-Prone Processes: The intricate nature of complex PCBs makes the design process susceptible to errors. Oversights and mistakes during layout, component placement, and routing can compromise product functionality and reliability. Undetected errors lead to revisions, rework, and possibly complete redesigns, impacting project timelines and budgets.

- Infrequent Checks: The labor-intensive nature of PCB checking processes discourages frequent checks throughout the design cycle. Delays in verification lead to accumulated errors and inconsistencies, making fixes challenging and time-consuming.

- Late-Stage Error Detection: Detecting design errors in later stages of development is inefficient, leading to more modifications, increased development time and costs, and delayed time-to-market. This is particularly critical in industries with rapid technological advancements.

- Simulation Challenges: Traditional signal and power integrity simulations involve analyzing numerous objects, including nets, planes, and area-fills. Collecting simulation models and running simulations for each object is labor-intensive and time-consuming, often exceeding the benefits gained.

HyperLynx DRC

To face these challenges, Siemens developed HyperLynx DRC, a rule-based checker that identifies potential PCB design errors using geometrical calculations. The key features are:

- Predefined Rules: The software comes with over 100 predefined rules addressing various aspects of PCB design, including signal integrity, power integrity, electromagnetic interference, electrostatic discharge, analog circuits, creepage, clearance, and IC package-specific checks.

- Efficient Embedded Engines: HyperLynx DRC utilizes various embedded engines, such as the geometry engine, graph engine, field solver, and creepage engine, for efficiently checking diverse technical challenges.

- Management of False Violations: The tool provides a feature for managing false violations, allowing users to create object lists, apply rules to specific objects, and eliminate unnecessary checks, significantly reducing checking time.

- Enhanced Filtering Capability: HyperLynx DRC enables the creation of object lists manually or automatically, offering filtering capabilities to focus on relevant objects.

The extensive capabilities of HyperLynx DRC can lead to long rule-based geometrical run times for large and complex designs. To address this, HyperLynx DRC provides the area-crop function, allowing users to isolate and analyze specific areas of the design.

The area-crop function streamlines the verification process through:

- User-Friendly Interface: Users can quickly specify an area by selecting nets or components using a wizard.

- Automated Cropping: The wizard automatically crops the design with predefined merging from the selected objects and creates a new project for checking.

This function enables users to concentrate on specific design areas, reducing complexity, enhancing accuracy and speeding up run times during verification.

Case Study

MediaTek, a leading semiconductor company, used HyperLynx DRC’s area-crop function on a highly complex board. The board specifications were:

- Layout file size: Over 300 MB

- Layers: Over 40

- Layout size: Over 22000 mil * 16000 mil

- Components: Over 16,000

- Nets: Over 11,000

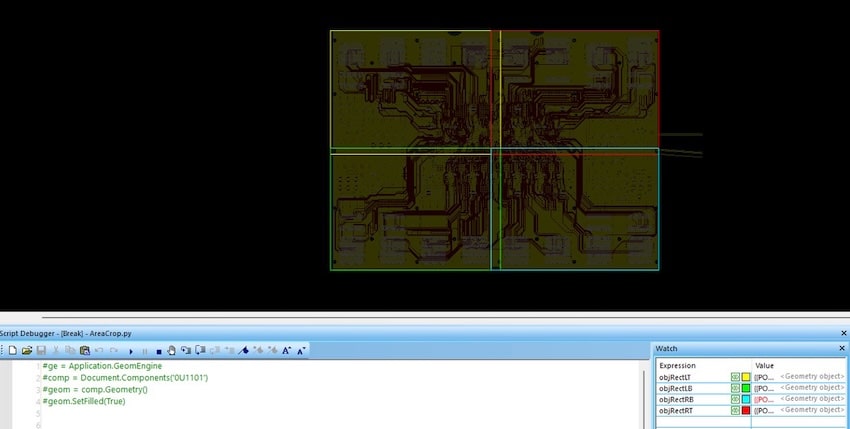

The area-crop function was used as follows:

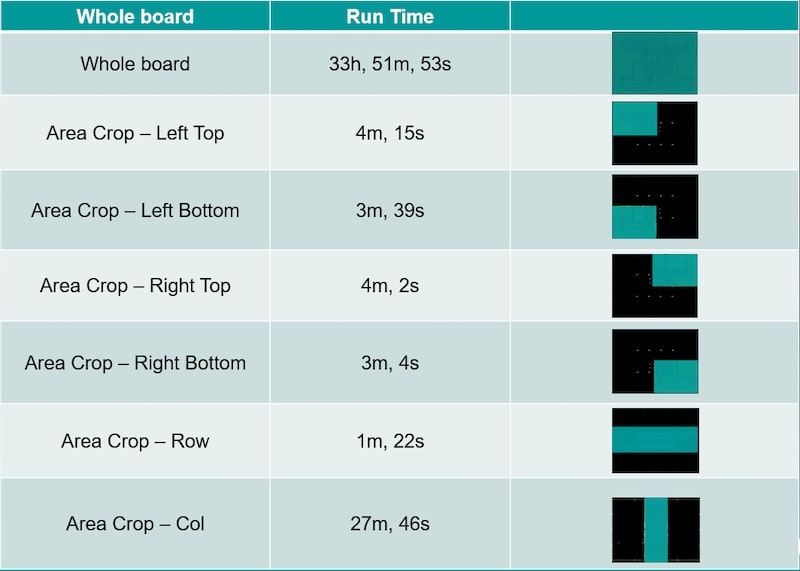

- Segmentation of the Board: The board was divided into four sections using vertical and horizontal virtual cuts, creating top-left, top-right, bottom-left, and bottom-right areas. Two additional overlap zones were added at the intersecting regions to ensure thoroughness.

- Accelerated Verification: Checking each section individually significantly reduced the overall run time, particularly for the complex GND signal Long Stub rule.

- Reduced Complexity: Dividing the board into smaller sections simplified the intricate GND nets, enhancing performance and allowing for efficient error identification and resolution.

The implementation of the area-crop function yielded impressive results:

- Time Reduction: Total checking time was reduced from 33 hours, 51 minutes, 53 seconds to just 44 minutes, a big time savings.

- Enhanced Efficiency and Precision: Focusing on segmented areas allowed for more precise verification, ensuring design reliability and integrity without compromising the project timeline.

- Optimized Resource Allocation: Large time savings and enhanced focus enabled optimized resource allocation, ensuring critical areas received proper scrutiny and facilitated a smoother design refinement process.

Conclusion

HyperLynx DRC’s area-crop function is a powerful tool for PCB design verification. By enabling focused verification, reducing complexity, and significantly accelerating the checking process, HyperLynx DRC ensures project success and meets the challenges of modern PCB designs. This innovative solution ensures advancements in electronic products are characterized by reliability, precision, and efficiency.

Read the complete, 12-page white paper online.

Related Blogs

- Next Generation of Systems Design at Siemens

- Discover the Future of HyperLynx Technology: Lunch and Learn

- Will my High-Speed Serial Link Work?

- Using PCB Automation for an AI and Machine Vision Product

- Cracking post-route Compliance Checking for High-Speed Serial Links with HyperLynx

- Mentor Automating Design Compliance with Power-Aware Simulation HyperLynx and Xpedition Flow

Comments

One Reply to “Electrical Rule Checking in PCB Tools”

You must register or log in to view/post comments.