Siemens EDA’s next move in its Calibre shift left strategy is the addition of correct-by-construction IC layout optimization for the most critical emerging physical design challenges. Calibre’s new DesignEnhancer product supports both custom and digital ICs and is already in use by several leading IC design companies. It targets three problem areas: optimization of vias, power grids and faster, higher quality decoupling capacitor and filler cell insertion.

But why get a signoff and verification tool involved in implementation and how is this better than the current P&R flow solutions ?

The principle’s nothing new – Calibre’s always had some design fixing capabilities. And it’s already tightly integrated with all leading layout flows.

But the critical reason is that layout tools aren’t always that good at some of the tasks they’ve traditionally been asked to do. Whether that’s slowness in the case of filler insertion or lack of precision in what they do – since they don’t have signoff quality rule-checking – meaning either later rework or increased design margining.

This matters on today’s highly complex designs and advanced process technologies. Users noticed the costs in design cycle time, quality and performance and pushed Siemens to make the Calibre capabilities available earlier in the flow where these were superior.

Via and Power Grid Optimization – Calibre DesignEnhancer Via & Pge

The importance of via resistance in leading edge processes makes more precise via implementation important. Designers need a more accurate picture of both timing and IR drop from the initial routing step. Leaving it any later means potential over-design for timing closure and late rework for IR drop and EM issues.

But that’s not possible without signoff quality DRC decks and rule checking. Hence Calibre’s new DesignEnhancer Via that supports both signal and power grid and via optimization by integrating Calibre into the layout flow both immediately after routing and with integrated incremental optimization after design ECO routes.

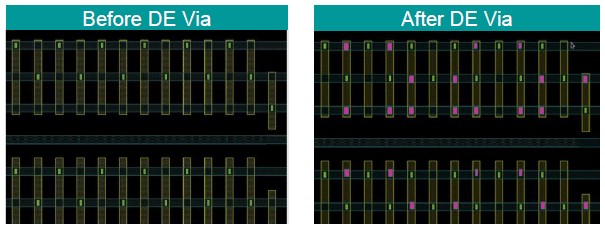

Siemens show a typical via optimization from DesignEnhancer Via below:

The improved version on the right clearly has more vias.

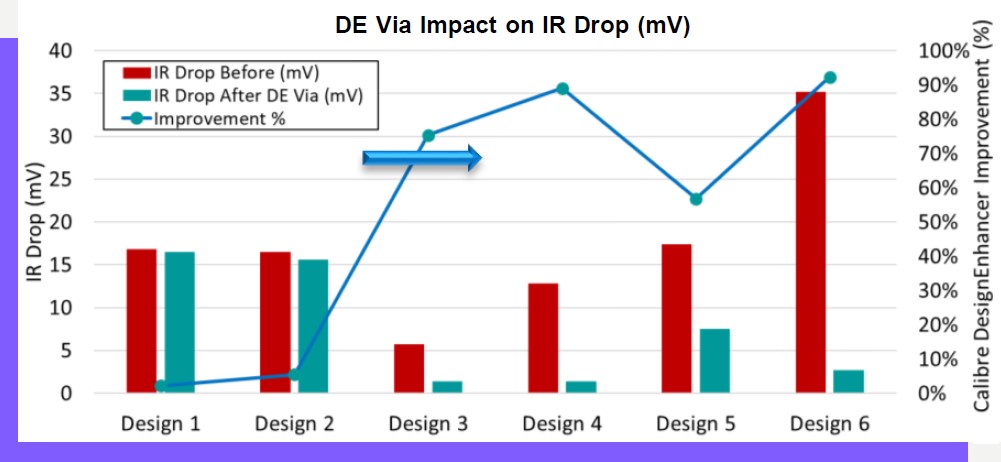

But the optimization isn’t limited to that – we also want to use the best possible vias (and perhaps in some local cases this means fewer). Layout tools can’t always make the best decisions here and may compromise. Calibre’s signoff quality DRC means that DesignEnhancer Via can do this. And that translates to more precise timing and reduced IR drop (particularly on SoC designs) as shown below:

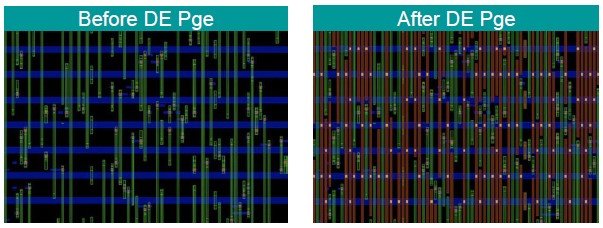

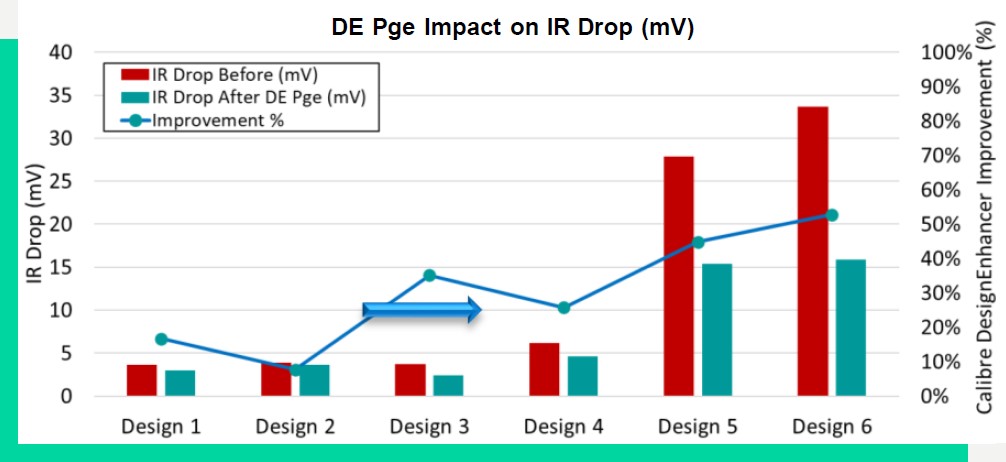

No one wants to get through to design signoff and find late EM and IR drop problems that a better power grid and power routing might have avoided much earlier in the flow. DesignEnhancer Pge (Power Grid Enhancer) provides optimization of already Calibre clean power routing for both interconnect wiring and vias so that a more precise power grid can be used from much earlier in the implementation flow.

This example shows the potential for inserting further power routing and reducing IR drop.

Again, results can show dramatic reductions in IR drop.

Better Filler and Decap insertion run time and quality – DesignEnhancer Pvr

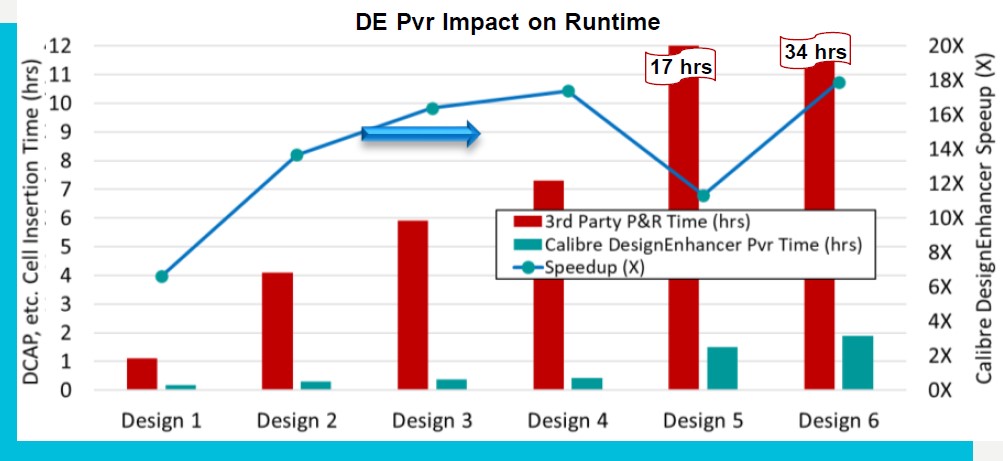

Inserting filler, decap and ECO cells has long been a painfully slow part of the P&R flow. But Calibre has always been able to insert these cells far more quickly and with more precise user control. Design Enhancer Pvr now shifts that capability back into those P&R flows.

Of course, none of that’s any real help if it doesn’t run any faster. Which it does – an order of magnitude faster – and that’s the full round-trip time from the layout tool DB:

Summary

Today’s increasingly complex design and process technologies are exposing gaps in the implementation design flow. Siemens is showing some real creativity in their shift-left strategy. What’s unique about the new Calibre DesignEnhancer product is the addition of automated, analysis-aware, Calibre correct-by-construction layout optimization at an earlier stage in the flow where it makes a real difference in reducing IR drop.

Customers already have results to prove this really does cut through to reduced design cycle time and better design quality. Design kits are available for the major foundries and supported for all major layout design flows (both custom and digital), which already have tight and efficient Calibre integration, making user adoption straightforward.

Siemens state their mission for Calibre is to make chip design to tapeout as fast and easy as possible for its customers – so it’s against that standard this product should be judged.

Expect to see more information from Siemens EDA following this product launch.

Also Read:

The Siemens Digital Industries Software View of AI and its Impact on System Design

Siemens Enhances Supply Chain Visibility with Real-Time Intelligence for its Xcelerator Platform

Transforming the electronics ecosystem with the component digital thread

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.