I first met Jimmy Chen from Easy-Logic at #60DAC and wrote about their Engineering Change Order (ECO) tool in August 2023. Recently we had a Zoom call so that I could see a live demo of their EDA tool in action. Allen Guo, the AE Manager for Easy-Logic gave me an overview presentation of the company and some history to provide a bit of context.

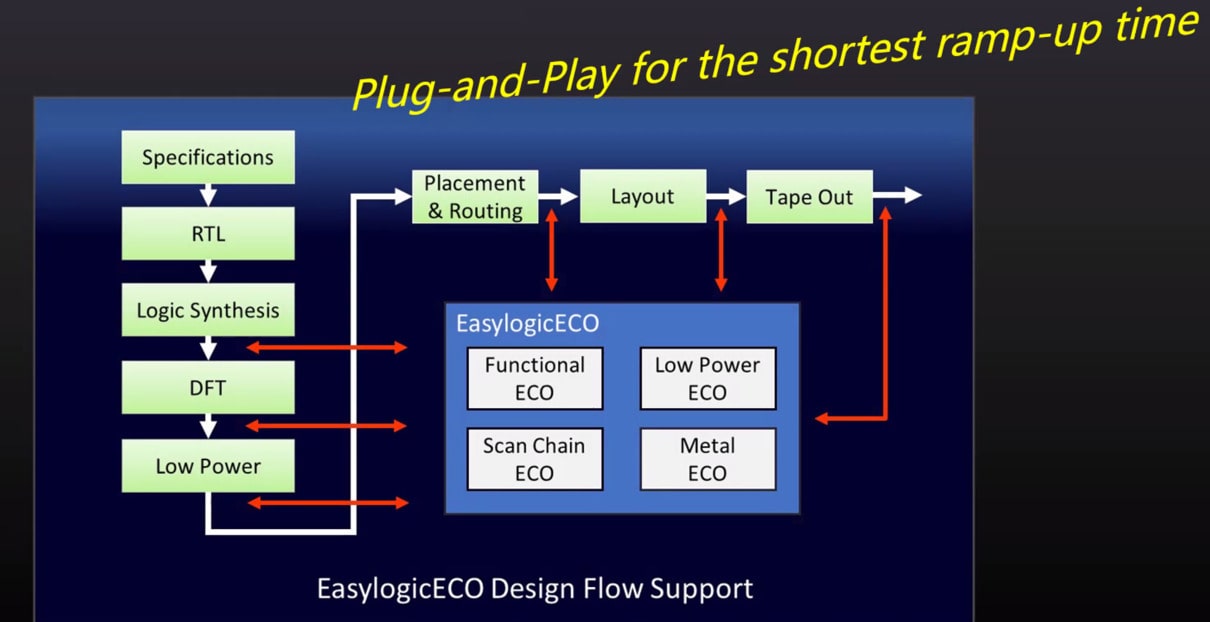

The company started 10 years ago in Hong Kong by a professor and students, they even won an ICCAD competition for an ECO test case in China, a nice way to get noticed. Their approach addresses making an ECO in four different places:

- Functional logic changes

- Low power changes

- Scan chain changes

- Metal connection changes

The challenge is to make an ECO with the smallest impact in a design flow to save both time and money. With the EasylogicECO tool you can expect to see the smallest patch size with minimum user effort, getting results in hours not days. Here’s the flow for using their tool.

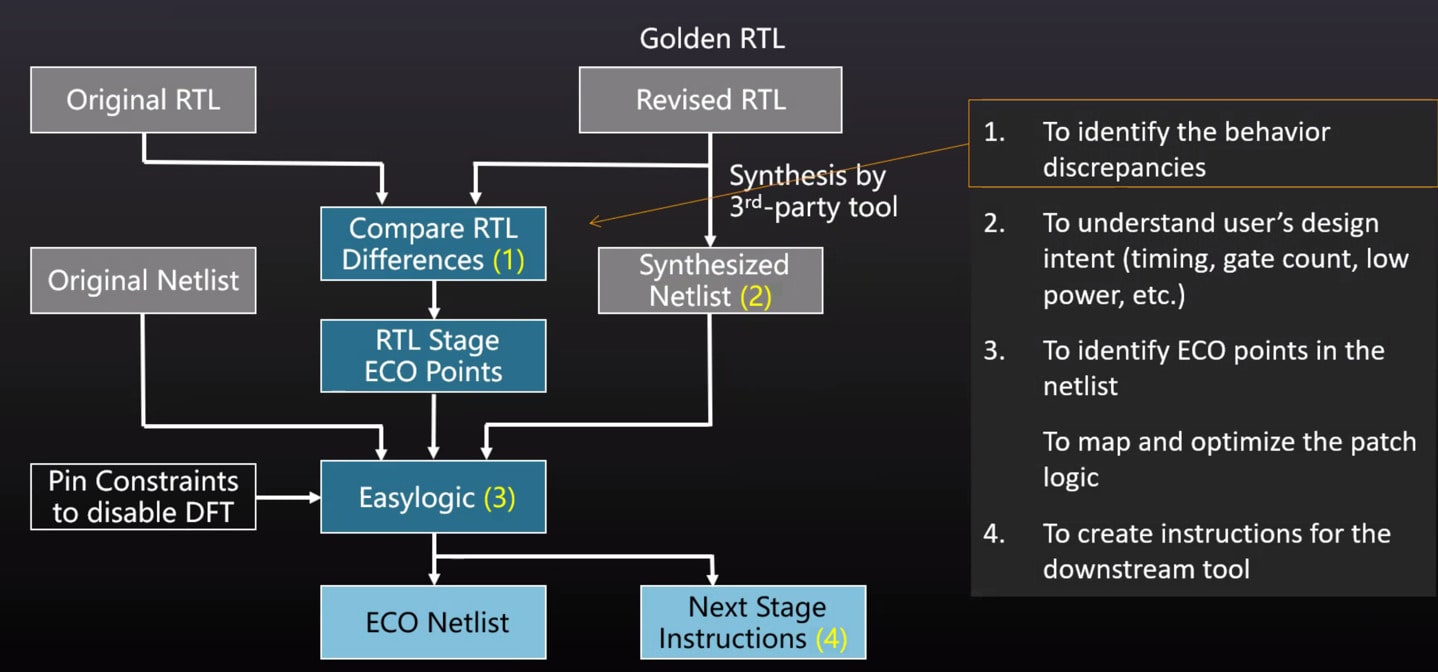

The tool compares two RTL netlists for differences, finds the modules with differences, and only modifies what is needed. By reading the entire design and only looking for what has changed enables EasylogicECO to be smarter than other ECO approaches, and there’s even formal checking of modules to ensure equivalence.

When making a Metal ECO there are lots of DFM and DRC rules to comply with, and EasylogicECO maintains logic levels in order to keep timing delays in place. There estimates to account for wire effects on delays, and the tool must pinpoint spare cells available to close timing and close routing. Users can run parallel ECO trials, then choose the best result. In the example below, versions 2 and 4 are better choices with the smallest patch sizes and smallest gate count changes.

I asked about the training time for an engineer to learn and become proficient at using EasylogicECO, and was surprised to hear that it only takes 30-40 minutes. Another question I had was about competition with other ECO tools, and they showed me a slide with multiple test cases that compared the patch size, where smaller is always better.

A smaller patch size greatly helps a project team to minimize the layers that need to be changed in metal, directly impacting the cost of mask rework. Each metal layer can cost in the millions for advanced nodes, so it’s important to use the minimum metal layers.

With other ECO tools a team has to add more spare resources to enable metal ECOs, which in turn causes a larger die size and higher silicon costs.

Demo

EasylogicECO is a batch tool run at the command line in a Unix environment. The first step is to generate script templates, then go to the scripts folder and decide which ECO script to run, and there are Readme files to explain the syntax and usage. Running each script will prompt the user for input files, like: Original RTL, revised RTL, module name, etc.

The demo test case took about one minute, running on a laptop computer. The script prompted for Verilog file names, module top, LEF file, DEF file, spare module name for metal ECO, spare cell naming and spare instance names. It then created scripts ready for logic synthesis and back-end tools like Innovus and ICC2.

Summary

All SoC projects experience last-minute changes which are threats to taping out on time and within budget. Finding bugs in silicon that require another spin will be expensive, so anything that can make this process go faster and cost less is welcomed. If your ECO process is taking weeks or months, then it’s high time to consider a newer approach to save valuable time and money.

Consider an evaluation of EasylogicECO and compare their approach with your previous methods to find out how much quicker an ECO can be done. Their ECO flow works with Cadence and Synopsys tools, so there’s no need for a CAD team to integrate anything as you can get patch results in just hours. Stay tuned for an upcoming webinar and if you’re attending #61DAC in June, then stop by their booth to get all your questions answered in person.

Related Blogs

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.