Nowadays, low power design requirements are key for large SoCs (system on chips) for different applications: AI, Mobile, HPC, etc. Power intent management early in the design flow is becoming crucial to help facing PPA (Power Performance Area) design challenges.

With the increasing complexity of such designs including challenging power optimization requirements, power intent should be managed right from the start through the design assembly process. RTL & power intent management requires nowadays to be less painful and with a higher degree of automation.

Indeed, a seamless and joint RTL & power intent integration process is beneficial at different levels knowing that power intent management is tightly correlated to the RTL integration process and vice versa. This is mainly explained by the numerous interactions which are needed between logic (RTL) and power intent (UPF) during the building processes and the correlation between RTL and power intent files. Consequently, a joint flow seems to be the good approach to avoids back and forth iterations between SoC/RTL and power engineers.

This joint flow must be able to cope with different scenario and maturity levels of the design project, such IP cores which have or not UPF files, missing power intent definitions at both IP and top levels between RTL and UPF, etc. with almost press button fixes.

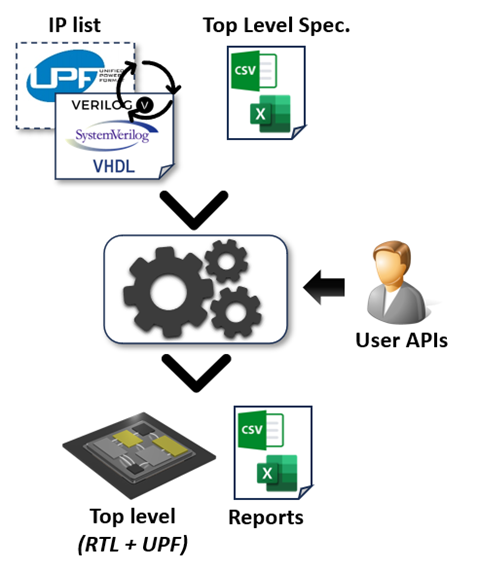

The ultimate goal of the tight integration processes is to generate top level, for both RTL and UPF views, ready for synthesis and simulation. A joint flow should be easy to use in order to enable even non-UPF experts to run the overall logic and power intent integration process.

Key automated capabilities are expected from such a joint RTL & UPF flow as summarized below.

- RTL vs UPF vs libraries consistency checks

It is key to detect early any inconsistency between logic design and power intent descriptions, including design libraries and any source of information which covers power intent attributes. Such checks need to be applied at both IP and subsystem levels. A typical example is a port naming mismatch between an RTL and a UPF file (for one or several power control signal). Another one is a missing power attribute a liberty cell and UPF, etc.

- Enable fast design learning

Since the joint flow is intended also for non-power experts, design learning capabilities need to be provided though simple APIs to help exploring existing power intent information (power state tables (PST), power switching strategies, etc.) including 3rd party IP cores and subsystems. During the learning process, designers should be able to easily catch missing power intent information such as power definitions and rules.

- Cross reporting APIs between RTL and UPF

As a joint flow, this should enable to provide cross reporting queries between RTL design and Power intent information. As a typical example, reporting the list of instances with the related power domains and associated supplies will really help designers to understand the correlation between RTL and UPF.

Of course, the related APIs should be intuitive for designers and straightforward.

- Automated Check & Fix capabilities

The flow should leverage check & fix features between RTL and UPF files. An incoherent name for instance would lead to a press button fix with an automatic update and file generation. Any fix should be automatically reflected from RTL to UPF and vice-versa. Also, power attributes from technology libraries need to be correctly reflected into the generated UPF files.

The power intent consistency must be checked at any time to ensure its completeness. Typically, the detection of missing level shifters and dangling supplies must happen the earliest in the flow to prevent further issues.

Finally, any RTL editing event like adding a new port, renaming a signal or other, should automatically lead to a UPF update.

- UPF generation at any hierarchical levels

Once the UPF for all the IPs is validated, the Top level UPF needs to be generated. No designer wants to write the Top level UPF manually. Starting from a clearly specified/captured power strategy, the UPF should be generated press-button.

- Consistent RTL/UPF hierarchical manipulation

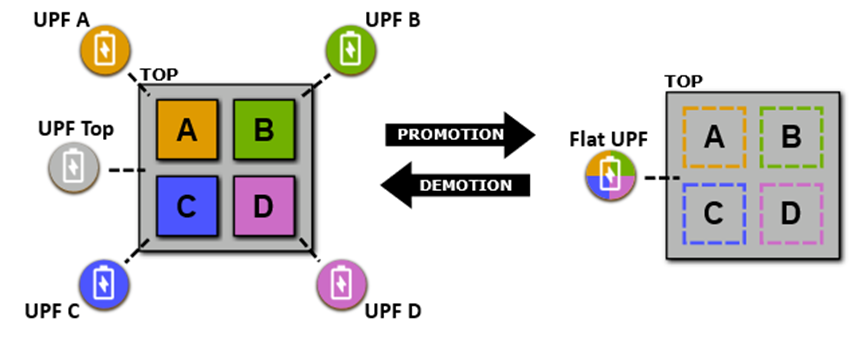

As RTL hierarchical changes need to be automated, the same expectation is required for power intent. In a divide and conquer design strategy with physically awareness, hierarchical manipulation is expected to help in many situations such as parallel synthesis, RTL with UPF simulation, etc.

- Enable efficient Design reuse & data extraction

Power intent needs also to be considered in a reuse process when building new SoC subsystems. Both RTL and UPF require smooth and automated extraction for a particular subsystem specification. UPF promotion and demotion capabilities are subsequently expected to help in this reuse process.

With its 20 years of expertise in RTL management and more than 10 years in UPF support, Defacto Technologies is providing a mature design solution to answer above needs and requirements from a joint RTL and power assembly flow.

Defacto’s SoC Compiler with its major release 10 covers all of the above requirements regardless UPF versions and RTL languages.

This solution joint RTL & power intent assembly flow pre synthesis is silicon proven and already got excellent results in particular on the UPF promotion and demotion.

Defacto will be holding a webinar by next week (December 14 at 10:00AM PST) where the Defacto experts with present a complete joint RTL & power intent assembly flow including all the steps describes above in the blog:

Following the webinar, a Whitepaper will also be available covering detailed explanations on the different steps of the joint flow through a typical design use case.

If any questions or to give a try to this joint flow, the Defacto team can also be contacted through their website: https://defactotech.com/contact

Also Read:

Defacto Celebrates 20th Anniversary @ DAC 2023!

Defacto’s SoC Compiler 10.0 is Making the SoC Building Process So Easy

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.