EDA has always been a fiercely competitive market, no more so than in emulation where the clash of claims and counter-claims can leave those of us on the sidelines wondering who’s really on top. Sales are the obvious indicator but leadership there flips back and forth between product releases. That makes Mentor’s choice to play a long game all the more interesting. This week they announced their Veloce Strato platform, raising the bar on specs again but also positioning this as the first step in a 5-year plan. When did you last hear of a 5-year plan from an EDA company?

Jean-Marie Brunet (Sr. Director of Marketing at Mentor) told me they had started with a study of capacity needs, stretching out to 2021. They see need to support up to 2.5 billion gates today and they have charted sizes, based on semiconductor company announcements and internal analysis, up to 15 billion gates 5 years from now. These monster designs are found where you would expect – CPUs, GPUs, APUs (application processing units in smartphones) and NPUs (network processing units) – possibly multi-die or multi-chip, maybe single die if EUV ever goes mainstream.

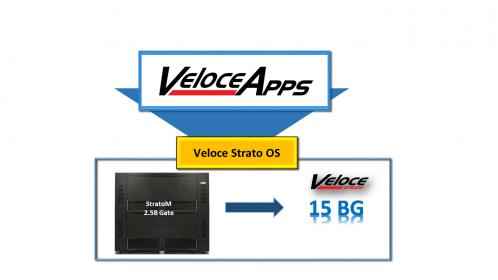

To get reasonable run-time performance, a design must fit in a single emulation box, whatever that box may contain. In light of these capacity projections, Mentor felt they had to move to a new architecture; Jean-Marie casts this as an evolution of the Veloce2 architecture rather than a revolution but significant enough that it can rise to these demands. This week they announced the Veloce Strato platform, designed to scale all the way to 15 billion gates, and availability of the Veloce StratoM emulator at 2.5 billion gate capacity as the first step in this plan.

Together with the Veloce Strato OS, designed with the same objective in mind, the new Veloce StratoM system delivers some impressive stats:

- 2.5x the capacity of Veloce2

- Up to 3x improvement in compile times with 100% success rate

- Up to 10x improvement in time to debug/visibility

- Up to 3x co-modeling speed improvement

- Overall, up to 5x improvement in throughput (compile-run-debug).

Strato OS has been designed to be platform independent and remains compatible with Veloce Apps and protocol solutions; it is also interoperable across legacy Veloce installations (Jean-Marie didn’t say how far back), as well as with Strato solutions. The StratoM fits in the aisle of a datacenter at 4-4.5 racks high and remains air-cooled. And StratoM boxes can be linked through StratoLink to further extend multi-user support.

Strato OS in many ways is the centerpiece of the Veloce Strato architecture. Of course, it must maintain compatibility and transparency across different Veloce architectures, but it also needs to offer support across multiple use-modes (ICE, accelerated testbenches, virtual components and others). Most important, it must integrate support for debug capabilities like Replay and LiveStream. This cross-platform support is a big part of what ensures scalability in the solution.

Applications for emulation beyond functional verification are multiplying in areas like software development and debug, power estimation and test debug. These capabilities will also scale with the platform. And there’s another compelling application where this level of emulation horsepower is already starting to become important – validation. We tend to think primarily in terms of verification when we think of EDA hardware, but validation (does the system operate as expected, not just does it conform to the spec) is just as important. Mentor has already taken a step in this direction in their partnership with Ixia, to model realistic network traffic. They anticipate, and they can hardly be wrong, that pre-silicon validation along these lines can only become more important across a wide range of designs. That will for them drive Strato OS as a common platform for verification, prototyping and validation solutions.

Naturally Mentor already has a StratoM customer and, just as naturally, it’s a customer who doesn’t allow their name to be used in press releases. But given the class of designs requiring this kind of box, it doesn’t take a lot of thought to narrow down the list of possibles. Feedback from that customer has been very positive and it sounds like other customers are now starting to use StratoM.

Putting this all together, Mentor has laid out a path to support scalable emulation of 15 billion gates within 5 years, they have redesigned hardware and software to meet this goal and have delivered the first step on that path, Veloce StratoM, proven with at least one large customer. And finally, the solution requires no disruption to existing Veloce customer flows, apps or protocol modeling; a run on StratoM just appears to be on a bigger and faster resource. That looks like the start of a well-executed long-game.

Share this post via:

Comments

0 Replies to “Mentor Plays for Keeps in Emulation”

You must register or log in to view/post comments.