In the early days of IC design there were arguments against using any extra transistors or gates for testability purposes, because that would be adding extra silicon area which in turn would drive up the costs of the chip and product. Today we are older and wiser, realizing that there are product pricing benefits to quickly test each new SoC before packaging and even in the field. The biggest annual event in the test world has to be the International Test Conference (ITC), coming up November 15-17 in Fort Worth, Texas. I was able to speak with Ron Press of Mentor Graphics by phone about what they are doing at ITC this year. Here’s an overview:

- Keynote by Wally Rhines, The Business of Test: Test and Semiconductor Economics (Tuesday, Nov 15, 9AM)

- Tutorial 5, Diagnosis-driven Yield Analysis (Sunday, Nov 13, 1PM – 4:30PM)

- Tutorial 9, Mixed-signal DFT and BIST: Trends, Principles and Solutions (Sunday, Nov 13, 1PM – 4:30PM)

- Session 2.1, Test point Insertion in Hybrid Test Compression/LBIST (Tuesday, Nov 15, 2PM – 4PM)

- Session 2.4, Minimal-Area Test Points for Deterministic Patterns

- Session 17.1, Automated Measurement of Defect Tolerance in Mixed-Signal ICs (Thursday, Nov 17, 1:30PM – 3:30PM)

Full details of Mentor at ITC are online here. By the way, Ron is the General Chair for ITC 2016. The big three themes that I learned from Ron about testability this year were:

[LIST=1]

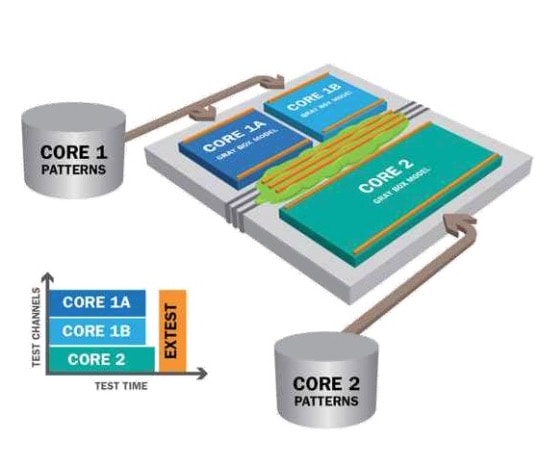

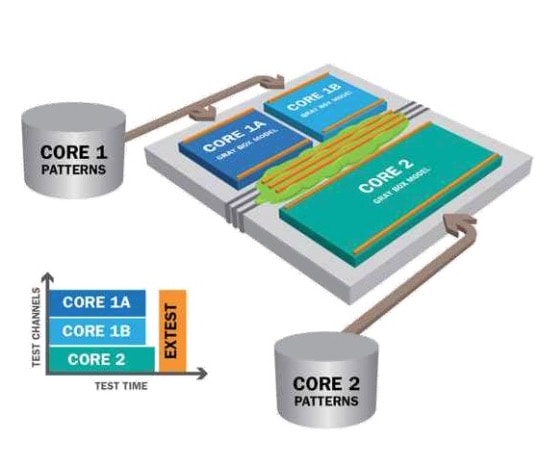

Our present era has now enabled SoC designs with billions of gates, so how are you going to test that kind of a chip in a reasonable amount of time? The answer is to divide and conquer, applying the concept of hierarchical test to reduce ATPG run times, minimize RAM usage, and actually generate ATPG results much earlier in the design flow. This methodology lets test engineers create and validate patterns for each block, then automation enables reuse of the patterns as each block is placed in an SoC.

Mentor also offers Embedded Deterministic Test (EDT) points that works with test compression to further reduce pattern volume giving you 2X to 4X additional compression on top of what their TestKompress approach offers.

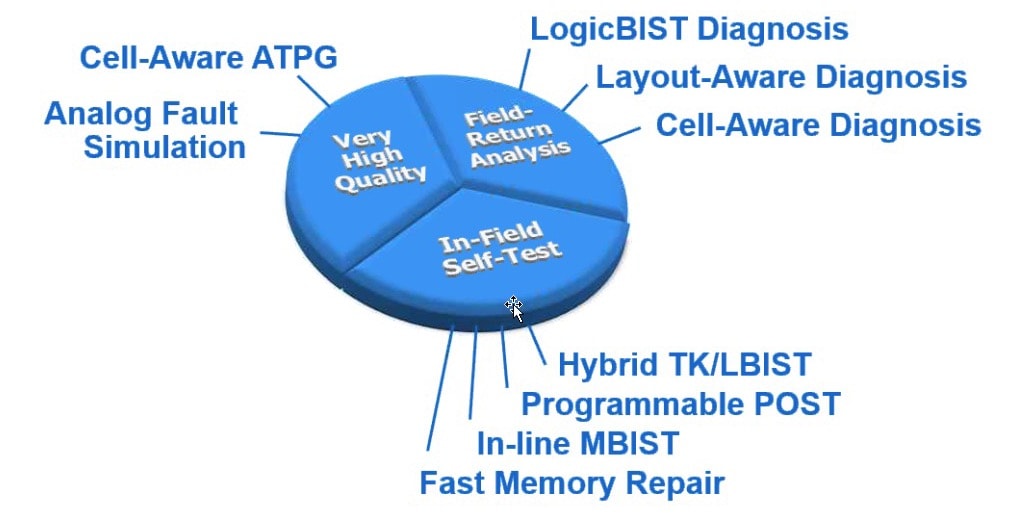

In the automotive world reliability of electronics is paramount, so they’ve created a standard called ISO 26262 and the EDA and semiconductor IP vendors have responded with both memory and logic BIST approaches. Field return analysis (RMA) is another key requirement for automotive. Mentor has created much of the test technology to meet the strict automotive requirements:

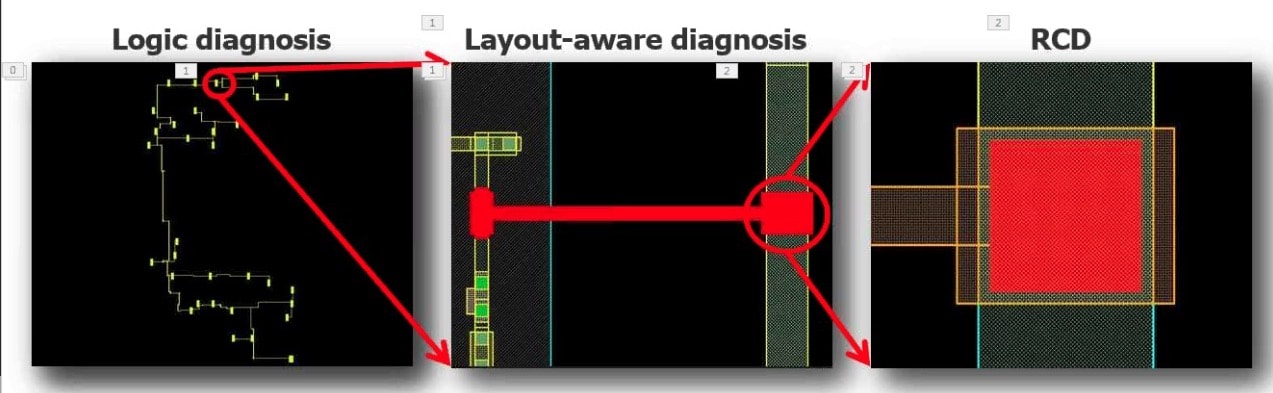

The final of three major points is diagnosing faults in FinFET technology, where the challenge is to identify the root cause of a particular type of physical failure. The three letter acronym they use is called Root Cause Deconvolution (RCD) and this technique uses statistical enhancement to pinpoint failures starting from the logical diagnosis and ending up at the layout location:

Transistor-level defects in FinFET designs can be located using cell-aware diagnosis for all of the pattern types (stuck-at, transition faults, cell-aware, etc.). The tools look at the FinFET layout and circuit schematic, then creates a cell-aware fault model specific to FinFET. Mentor has been using this sophisticated fault modeling since the 32nm node and smaller.

If you attend ITC this year then consider checking out what the actual users of Mentor tools are talking about in their test experiences at the Posters: Samsung, Teradyne, Spreadtrum.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.