Semiconductor design automation at system level is gaining its due importance today. It needs an effective, efficient, and seamless flow from system up to silicon. There is lot of effort going on for automating SoC design exploration at system level but that eventually stops at RTL; another level of flow automation takes over from RTL to physical implementation, and then to silicon.

Traditional flows from RTL to physical design are inefficient because of long iterations involved between gate-level physical implementation and RTL; sometimes it becomes time-prohibitive or impossible to correct the design at RTL but live with inefficient work-around at gate-level. This is because RTL synthesis doesn’t have physical information until the gate level implementation. Synthesis tools and Floorplanning which ties together the front-end design at RTL level and back-end design at gate-level rely on inaccurate RC and physical models.

As the design sizes are increasing and moving up to system level, it is utmost important and more reason for RTL-to-Gate level flow to become less iterative and be more decisive with accuracy at RTL level to the extent that design signoff can be done at RTL without waiting until physical implementation. A decisive floorplanning tool at RTL level can very well facilitate design prototyping, SoC full-chip planning, as well as IP signoff at RTL level.

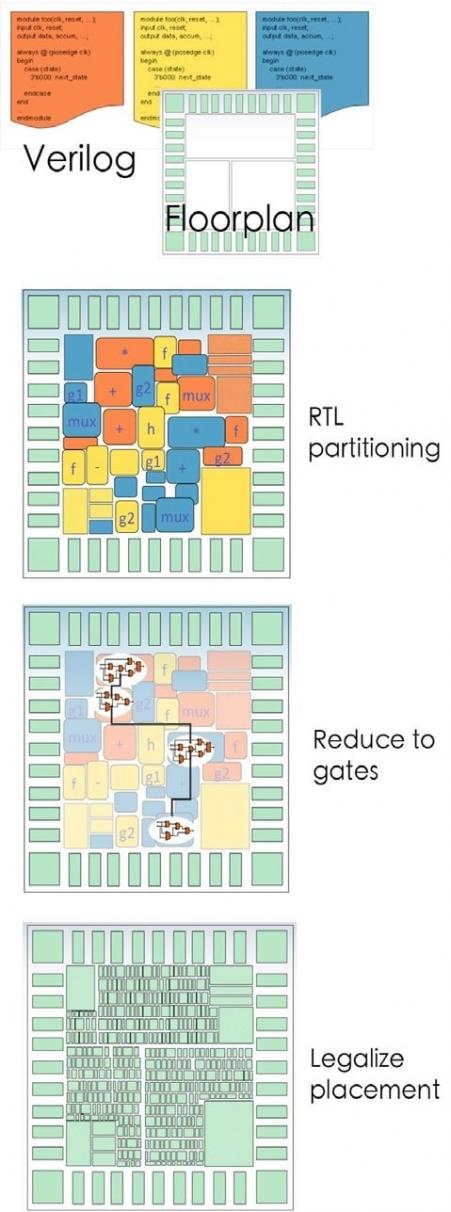

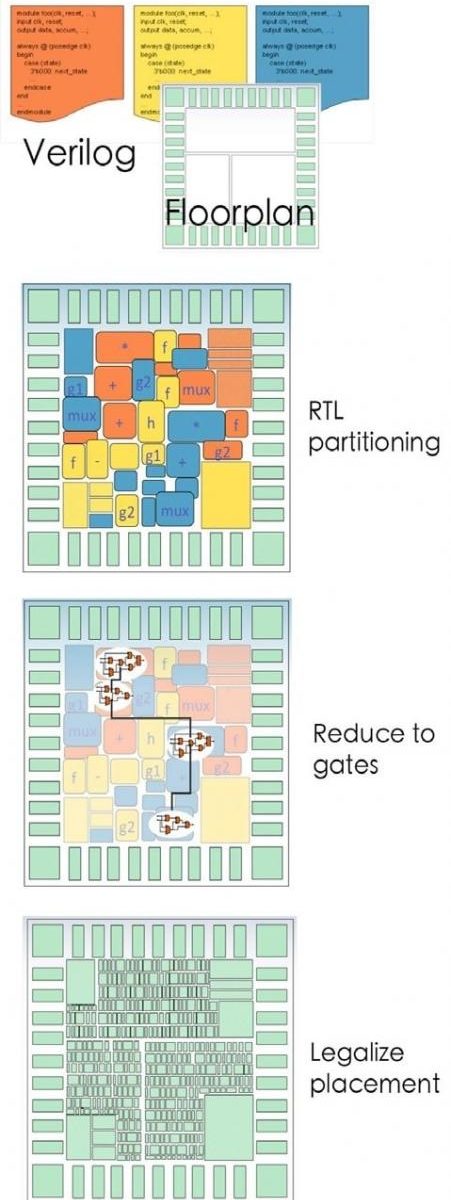

I like Mentor’snext-generation physical RTL synthesis and floorplanning tools including RealTime Designer[SUP]TM[/SUP] and other products. The floorplan is created at the RTL level based on the high-level RTL modules, macros, and design data flow. This enables high-level design optimization and accurate timing and congestion analysis. Incremental changes can be done to the floorplan to adjust PPA (power, performance, and area), congestion and routability.

Physical hierarchies are honored and RTL partitions are correctly assigned within the physical boundaries of the appropriate partitions. Mentor’s patented technology is used to access the detailed netlist of each RTL partition to accurately time the design. The synthesis and floorplanning with real physical and timing information makes the flow reliable and predictable, thus reducing the number of iterations and time to design closure.

The floorplan from RTL can be generated either automatically or incrementally by placing macros and assigning pins according to the constraints such as die size, macros, pin locations etc. provided by the user or supplied in a DEF (Design Exchange Format) file.

The designer can perform fly line and connectivity analysis between regions before placing physical partitions. The regions can be shaped and sized automatically depending on the die size and utilization constraints. All advanced floorplanning features such as fences, blockage, physical guidance, and rectilinear boundaries for space optimization are enabled.

To implement an efficient and testable design, scan insertion can be done during synthesis which enables early debugging of test problems and allows better scan architecture, reduced length of scan nets, and improved routability. Mentor’s tools are very efficient; a design with 10 million instances that might contain 1 million flops can be processed for scan analysis in 10 minutes and scan insertion in 20 minutes.

The advanced physical modeling techniques used during RTL synthesis provides very close correlation to P&R system; timing correlation comes within 5% of Mentor’s P&R system. This provides confidence in synthesis and floorplanning QoR and naturally minimizes the back-end to front-end iterations. Some of the actual experimented results are can be found in a whitepaper at Mentor’s website.

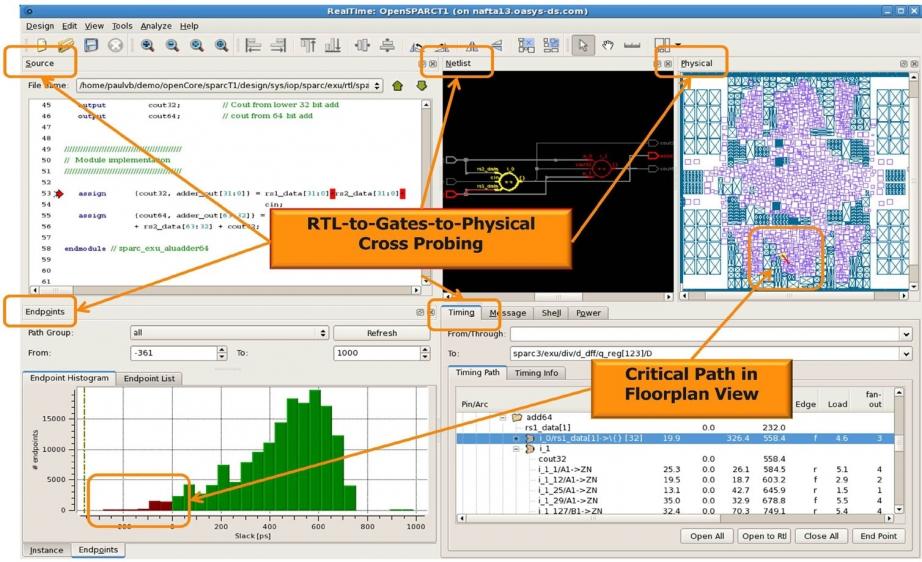

Mentor’s physical RTL synthesis and floorplanning tools are provided with a powerful integrated cockpit where cross-probing can be done easily between RTL and physical databases associated with different design views (logical, physical, or timing). The static and dynamic power map, congestion map, timing map, and hierarchical floorplan view can be debugged easily with different physical views. Any required changes can be done and synthesis re-run quickly to optimize the design.

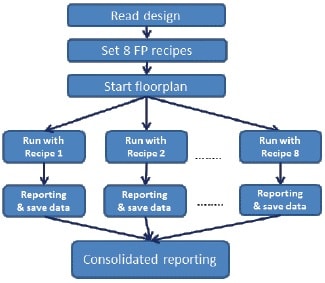

Mentor’s physical RTL synthesis and floorplanning tools come with high capacity and speed that can enable multiple parallel floorplan explorations with different recipes for design alternatives. The best configuration for implementation can be decided after analyzing results from all runs. The floorplan exploration report contains data such as TNS, WNS, instance-count, area, power, congestion, and wire-length.

The tools and full-chip flat run methodologies as described above in Mentor’s RTL synthesis and floorplanning system provide up to 10x higher performance compared to traditional physical synthesis tools, and also equal or better QoR (area, timing, placement, and production quality floorplan). Designs up to 100 million gates can be easily accommodated.

Arvind Narayanan has described the tools and methodology in detail with some impressive experimental results in a whitepaper at Mentor’s website HERE.

Pawan Kumar Fangaria

Founder & President at www.fangarias.com

Comments

0 Replies to “Decisive Floorplanning for Faster Design Closure”

You must register or log in to view/post comments.