Semiconductor design automation at system level is gaining its due importance today. It needs an effective, efficient, and seamless flow from system up to silicon. There is lot of effort going on for automating SoC design exploration at system level but that eventually stops at RTL; another level of flow automation takes over … Read More

Tag: realtime designer

Not All RTL Synthesis Approaches are the Same

My first experience with logic synthesis was at Silicon Compilers in the late 1980s using a tool called Genesil. Process technology since that time has moved from 3 um down to 20 nm, so there are new challenges for RTL synthesis. Today you can find logic synthesis tools being offered by the big three in EDA: Synopsys, Cadence, Mentor… Read More

Mentor Buys Oasys

Mentor is acquiring Oasys, subject to all the usual caveats about shareholder and regulatory approval. The shareholder paperwork went out earlier this week. The common stock is valueless so presumably the price is low (and Mentor historically has not paid high prices for its acquisitions).

So what is going to happen with the technology?… Read More

Floorplanning Merged With Synthesis

One area of iteration that is becoming more problematic is between floorplanning and synthesis. So much of timing is driven by placement that fixing timing and even power often involves not just re-synthesis and re-placement but alterations to the floorplan. The Achilles heel of existing methods is that floorplanning tools … Read More

Oasys Bakes a PIE

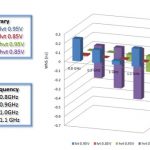

One challenge in building a modern SoC is that you want to minimize power, performance and area (PPA) while still getting your chip to market on schedule. Realistically, you can’t actually minimize all of these at once since they are tradeoffs: speeding up a critical path often involves upsizing drivers to larger cells which… Read More

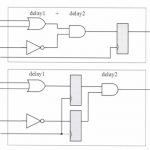

RealTime Register Retiming

I was at the EDAC CEO forecast meeting last week and one of the questions that was asked of EDAC members was “which is the hottest EDA startup?” The one with the most nominations was Oasys. So Oasys is hot.

But register retiming is hotter.

The latest announcement from Oasys this morning is that register retiming is now … Read More

Integrating Formal Verification into Synthesis

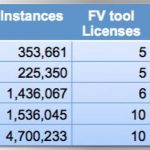

Formal verification can be used for many things, but one is to ensure that synthesis performs correctly and that the behavior of the output netlist is the same as the behavior of the input RTL. But designs are getting very large and formal verification is a complex tool to use, especially if the design is too large for the formal tool… Read More

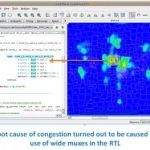

SoC Implementation, Sometimes You Need a Plan B

I read two blogs this week that got me to thinking about contingencies in SoC implementation. By contingency I mean using an EDA tool flow from the leading vendor for logic synthesis and then discovering that you cannot route the design without expanding the die size after a few weeks of concerted effort, then having to come up with… Read More

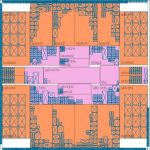

Chip Synthesis at DAC

I visited Oasys Design Systems and talked to Craig Robbins, their VP sales. For the first time this year, Oasys has a theater presentations and demos of RealTime Designer which are open to anyone attending the show. In previous years, they have had suite demos for appropriately qualified potential customers but outside they have… Read More