I was at the EDAC CEO forecast meeting last week and one of the questions that was asked of EDAC members was “which is the hottest EDA startup?” The one with the most nominations was Oasys. So Oasys is hot.

But register retiming is hotter.

The latest announcement from Oasys this morning is that register retiming is now available in the RealTime synthesis engine that underlies all of Oasys’s products. This is driven especially by Oasys’s customers designing high-performance graphics processors (GPUs) since these have very complex pipelines that are next to impossible to balance by hand in the RTL. However, it is also applicable to many other domains especially in communications.

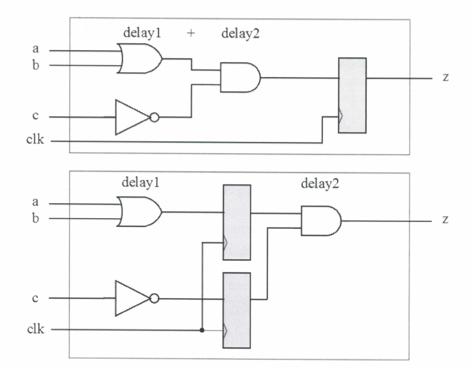

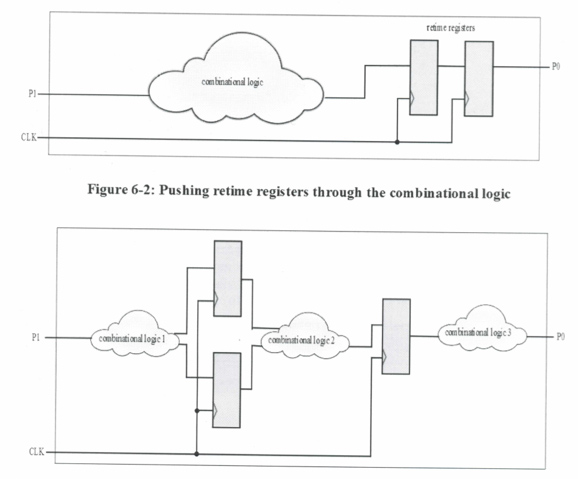

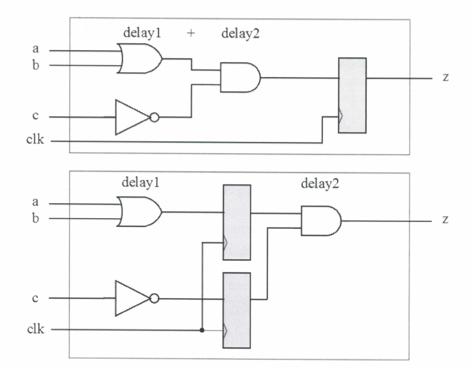

Register retiming involves moving logic from before a register to after (or vice versa) in a way that preserves functionality, but improves timing, power and/or area. For a datapath, typically this is attempting to balance the amount of logic between all stages of a pipeline so that the entire pipeline can be clocked at the ideal frequency, rather than being limited due to especially long paths in some stages. This may involve adding (or removing) additional registers, as in the example above, to hold intermediate values from in the combinational logic.

In fact it makes the design easier since extra registers can be added almost trivially to the design, typically at the end of a datapath or just after a large cone of combinational logic, leaving the synthesis engine to pull the registers into the logic cones (and duplicate them if necessary) in order to balance the clocks, as in the example above.

Note that although the behavior at the inputs and outputs is identical, the sequential behavior will not be identical in that the number of registers and the register contents may differ. A trivial example is pushing an inverter from before a register to after it. The final output will be the same but the contents of the register will be inverted from before.

Share this post via:

Solving the EDA tool fragmentation crisis