It has been about a year since the acquisition of Berkeley Design Automation by Mentor Graphics. Berkeley was doing quite well in the somewhat crowded SPICE simulator market. In many respects they broke new ground for high speed and accurate SPICE simulators. Since the acquisition we know that former Berkeley executives are now in significant roles at Mentor. Mike Ellow, former Berkeley Sales VP, is now Senior VP of Mentor’s World Trade Organization; and Ravi Subramanian, former Berkeley CEO, is now Mentor’s General Manager of the Analog Mixed Signal BU.

But more important than how the former Berkeley execs are doing, is how well the products from Berkeley are faring at Mentor.I had the pleasure of reading a white paper from Mentor on their Analog FastSPICE RF suite. The paper is written by two key members of the Berkeley team. David Lee was a co-founder of Berkeley Design Automation, and has a background that spans Bell Northern, Bell Labs and Lucent. The other author is Mick Tegethoff who has worked both in the semi industry and in EDA. He is responsible for marketing in Mentor’s AMSV business unit.

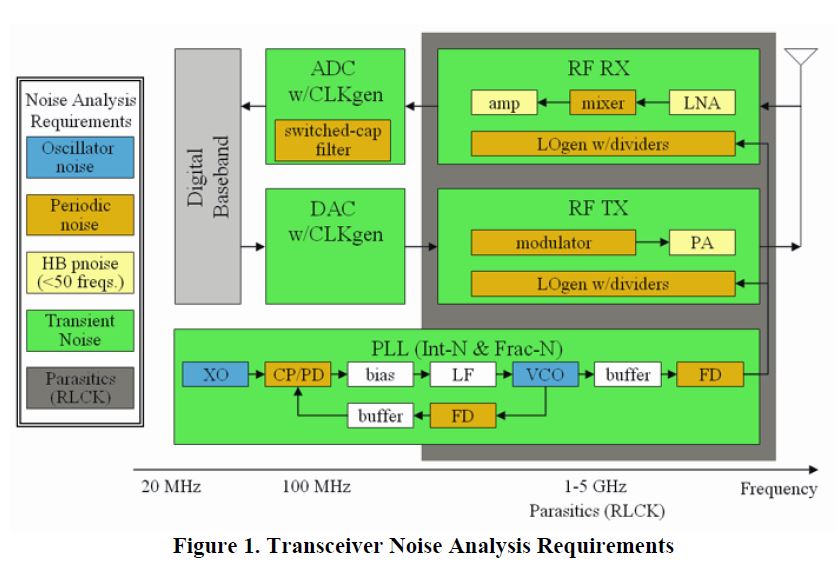

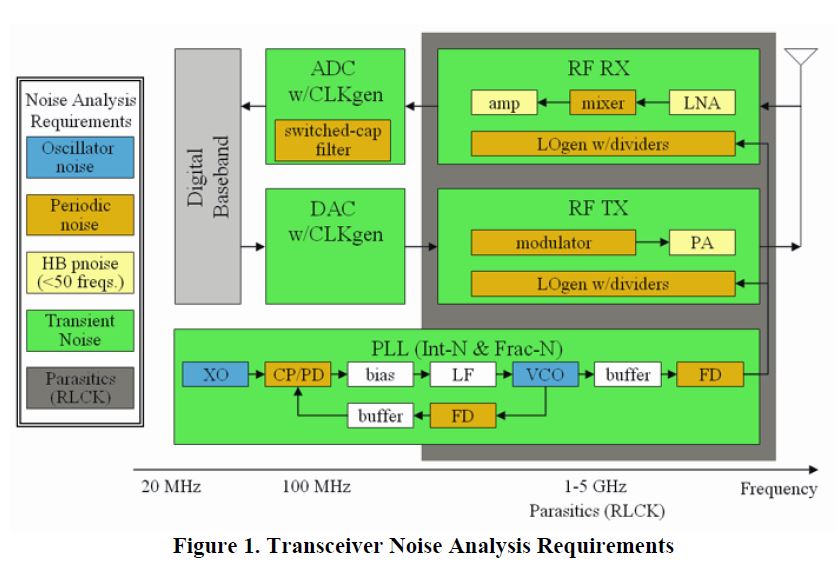

The paper, which can be found here, delves into the challenges faced by high speed analog designers who are increasingly required to work in bulk CMOS and at RF speeds. RF today really no longer implies just radio circuits: SerDes circuits often operate at over 20GHz – well above many RF circuits such as those in the 2.4 or 5 GHz range. The other problem facing analog RF designers is increasing complexity. The circuits have more devices, there are more circuits that must be analyzed concurrently (without making simplifications and approximations), and parasitics play an increasing role in circuit behavior and cannot be ignored.

As high speed analog circuits progress through the design process, their analysis needs progress as well. Estimated parasitics are added followed by device noise analysis and actual parasitics. Finally PVT variation needs to be considered as part of design verification. SPICE simulation is pivotal in each of these steps.

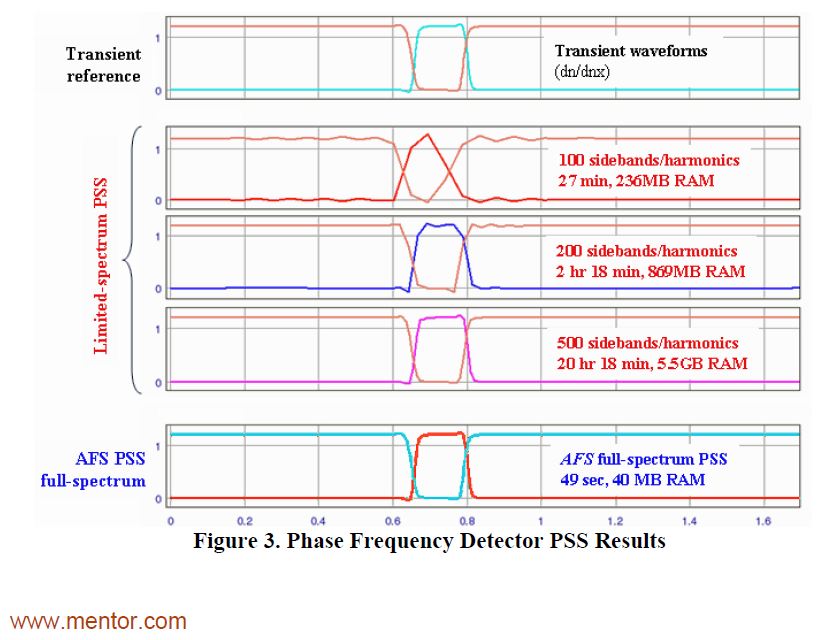

The Mentor white paper points out that Periodic Signal Analysis of near-linear circuits without sharp transitions can be analyzed using Harmonic Balance (HB) techniques. However designers must rely on time domain methods such as Shooting-Newton when the circuits have less linearity or have sharp transitions – which is happening increasingly. Nevertheless, achieving Periodic Steady State (PSS) convergence on the circuits is difficult for many traditional SPICE simulators.

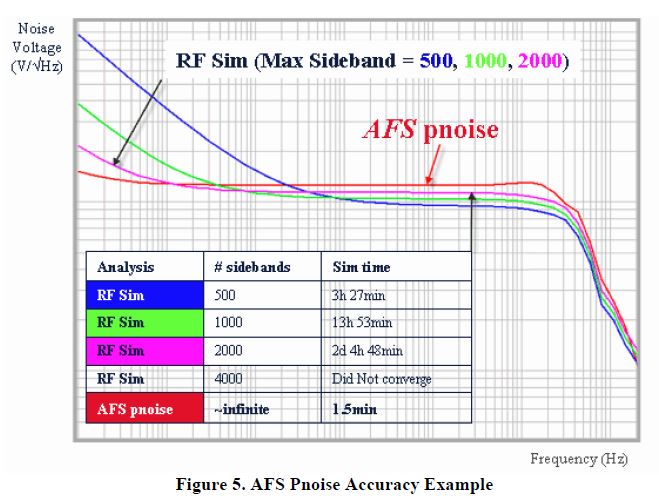

Mentor’s AFS has unique abilities that let it work effectively on non-linear circuits in the frequency domain. First, it uses a Direct Solver, instead of a Krylov based solver for HB. This improves convergence and dramatically improves performance. Secondly, AFS is able to use a full spectrum approach. Instead of limiting the harmonics, it includes noise effects from all the sidebands or harmonics. This graphic from the white paper illustrates how full spectrum simulation in AFS gives better transient results.

There is much more in the white paper. It goes on to talk about Noise Floor improvements in transient sims. Other sections discuss Periodic Device Noise Analysis, Transient Device Noise Analysis, and full parasitic simulation. It closes with more information on circuit characterization, including PVT effects. Lastly it goes over their multi-core parallel operating mode for getting faster results.

Designing at RF frequencies, be it for an optical, RF or a copper medium, is an increasing challenge, especially in bulk CMOS with ever tighter design criteria and specifications. Analog circuit simulation is a mainstay of this process. Mentor appears to have brought on board some key technology as it grows its investment in analog RF design tools and expertise. If you want to read the full white paper, it can be found here.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.