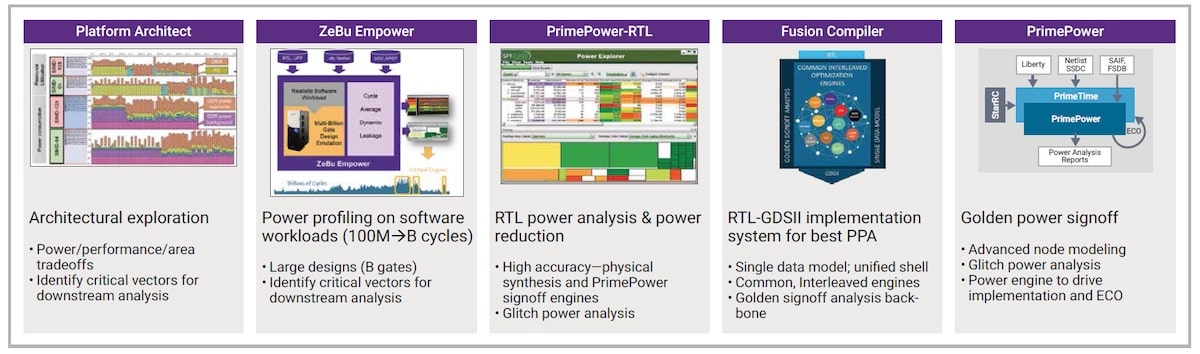

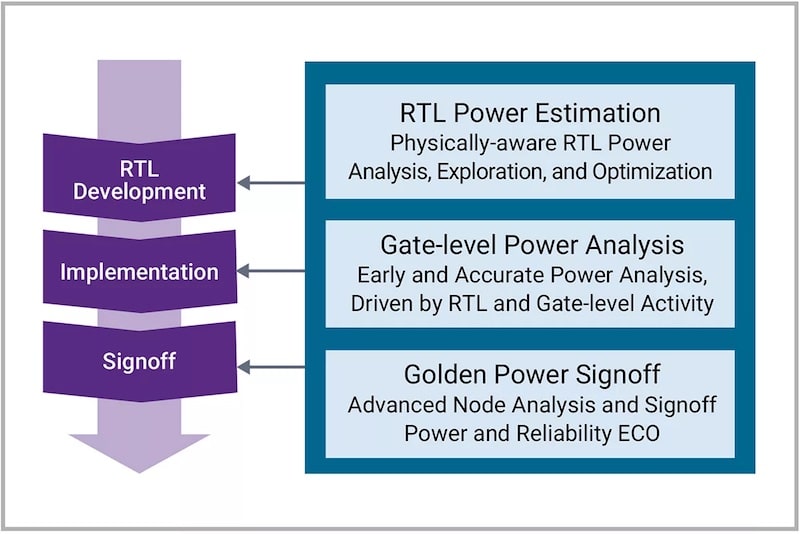

SoC designs use many levels of design abstraction during their journey from ideation to implementation, and now it’s possible to perform power analysis quite early in the design process. I had a call with William Ruby, Director of Porduct Marketing – Synopsys Low Power Solution to hear what they’ve engineered across multiple technologies. Low-power IC designs that run on batteries need to meet battery life goals, and that is achieved through analyzing and minimizing power throughout the design lifecycle. High-performance IC designs also need to meet their power specifications, and lowering power during early analysis can also allow for increased clock rates which then boosts performance further. There are five EDA products from Synopsys that each provide power analysis and optimization capabilities to your engineering team from software to signoff.

The first EDA tool listed is Platform Architect, and that is used to explore architectures and even provide early power analysis, before any RTL is developed by using an architectural model that your team can run different use cases on. With the Platform Architect tool you can build a virtual platform for early software development, and to start verifying the hardware performance.

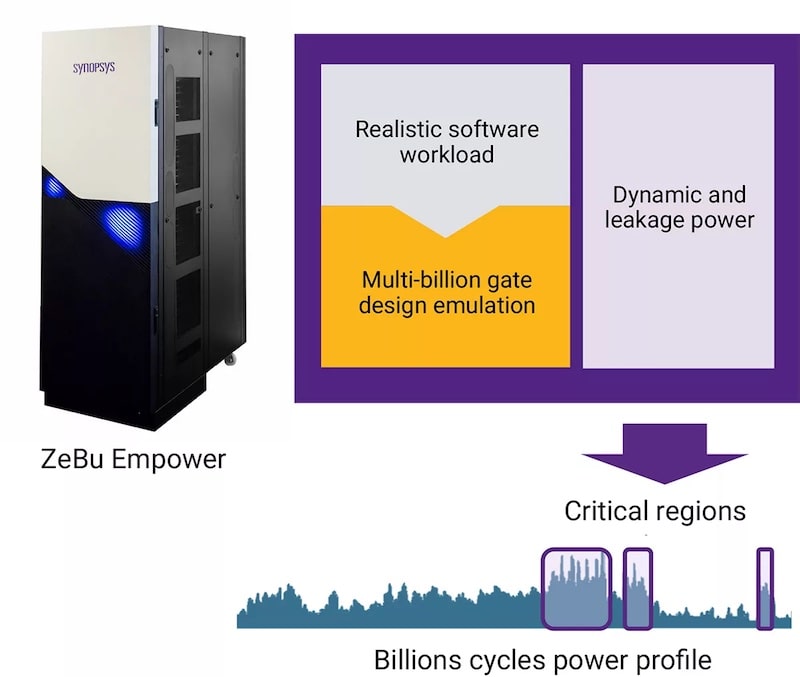

Once RTL has been developed, then an emulator like Synopsys ZeBu can be used to run actual software on the hardware representation. Following the emulation run, ZeBu Empower delivers power profiling of the entire SoC design so that you can know the sources of dynamic and leakage power quite early, before silicon implementation. These power profiles cover billions of cycles, and the critical regions are quickly identified as areas for improvements.

RTL Power Analysis

RTL power analysis is run with the PrimePower RTL tool using vectors from simulation and/or emulation, or even without vectors for what-if analysis. Designers can explore and get guidance on the effects of clock-gating, memory, data-path and glitch power. The power analysis done at this stage is physically-aware, and consistent with signoff power analysis results.

Gate-level Power Analysis

Logic synthesis converts RTL into a technology-specific gate-level netlist, ready for placement and routing during the implementation stage. The golden power signoff is done on the gate-level design using PrimePower. Gate-level power analysis provides you with average power, peak power, glitch power, clock network power, dynamic and leakage power, and even multi-voltage power. Input vectors can come from RTL simulation, emulation or vectorless. The RTL to GDSII flow is provided with the Fusion Compiler tool, where engineers optimize their Power, Performance and Area (PPA) goals.

Summary

Achieving energy efficiency from software to silicon is now a reality using the flow of tools and technologies provided by Synopsys. This approach takes the guesswork out of meeting your power goals prior to testing silicon, and has been proven by many design teams around the world. What a relief to actually know that your power specification has been met early in the design lifecycle.

Synopsys has a web page devoted to energy-efficient SoC designs, and there’s even a short overview video on low-power methodology. There’s also a White Paper, Achieving Consistent RTL Power Accuracy.

Related Blogs

- Multi-Die Systems Key to Next Wave of Systems Innovations

- Computational Imaging Craves System-Level Design and Simulation Tools to Leverage AI in Embedded Vision

- Optimize RTL and Software with Fast Power Verification Results for Billion-Gate Designs

- Webinar: Achieving Consistent RTL Power Accuracy

- Accurate Power Sooner

- Webinar: Optimize SoC Glitch Power with Accurate Analysis from RTL to Signoff

- Fusion Synthesis for Advanced Process Nodes

- Synopsys Fusion Compiler Delivers ARM Hercules-Samsung 5LPE Design

- Synopsys Low Power Workshop Offers Breadth and Depth

Comments

There are no comments yet.

You must register or log in to view/post comments.