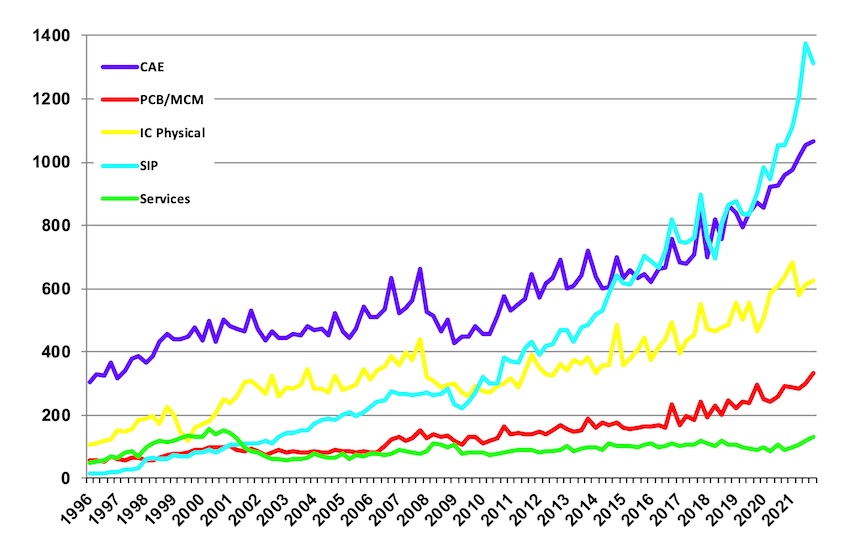

The ESD Alliance collects and reports every quarter the revenue trends for both EDA and Semiconductor IP (SiP), and the biggest component for the past few years has been the SiP, as IP re-use dominates new designs. For Q4 of 2021 the total SiP revenue was $1,314.3 Million, enjoying a 24.8% growth in just one year. Here’s a chart to better show the IP trend:

How are engineers re-using all of this IP in their designs? EDA, IP and systems companies created the SPIRIT Consortium back in 2003 to address IP reuse, and by 2009 this group merged with Accellera, so there’s a long history to standardize how IP is defined and reused with IP-XACT, an XML format. The first IEEE standard for IP-XACT was named 1685-2009, then in 2014 it was superseded by IEEE 1685-2014. Defacto Technologies has been offering EDA tools to use IP-XACT more efficiently for 10 years now.

SoC Compiler

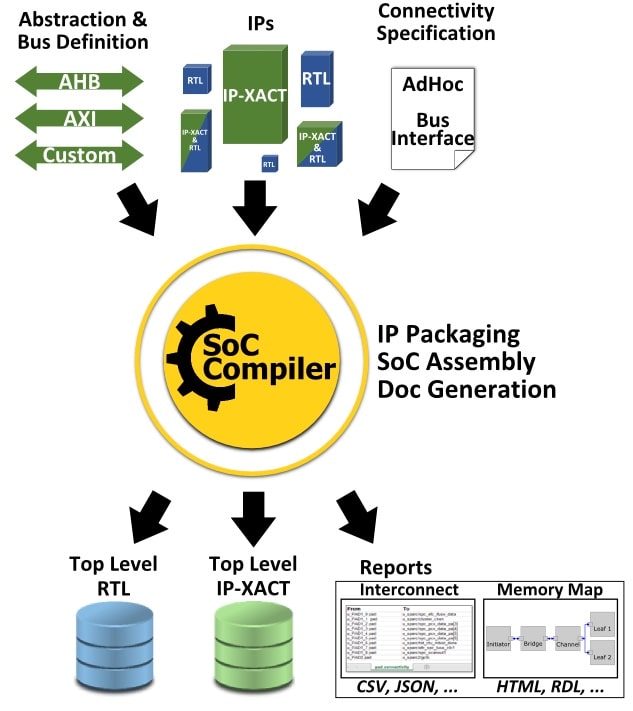

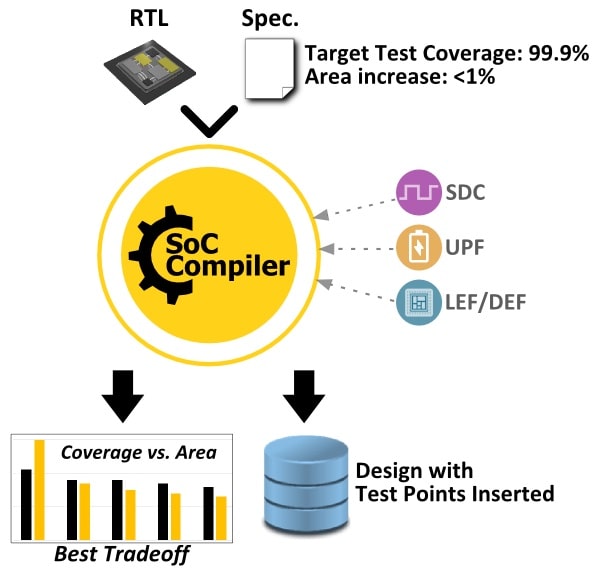

To integrate all of the IP blocks used in a new SoC design requires a methodology, and Defacto supports a front-end design flow that handles RTL, IP-XACT, UPF, LEF/DEF and SDC formats, getting your design ready for logic synthesis. SoC Compiler is the EDA tool from Defacto used for:

- Design extraction and reuse for existing projects

- IP connectivity insertion

- SoC creation and assembly

- Packaging at IP, subsystem and SoC levels

- Generation of RTL, IP-XACT and other design collaterals

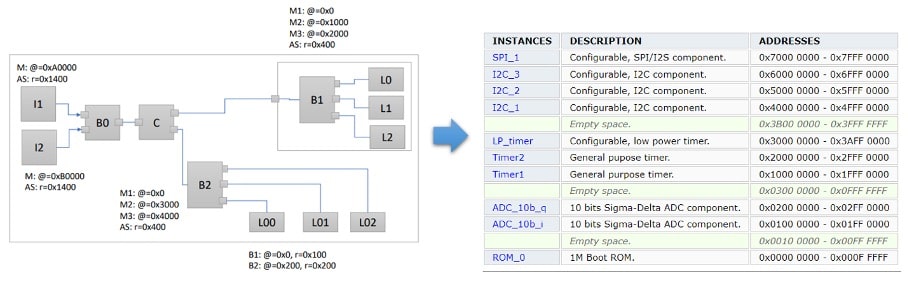

SoC Compiler fully supports both the 2009 and 2014 versions of IP-XACT, so it works with all IP provided by vendors. A new feature in SoC Compiler is the ability to automatically extract the system memory map. Here’s an example of how RTL blocks on the left are turned into a memory map on the right, saving you time by not requiring any manual updates.

Connectivity Insertion

During SoC assembly there is connectivity insertion, where all of the IP blocks are connected, then creating connections between different ports. An input port for source and destination port for recipient need to be connected. This process is now highly complicated because of the number of connections that are expected. Using SoC Compiler manages automatically the interconnect used between AMBA AXI and other standard interfaces, just by reading RTL and IP-XACT.

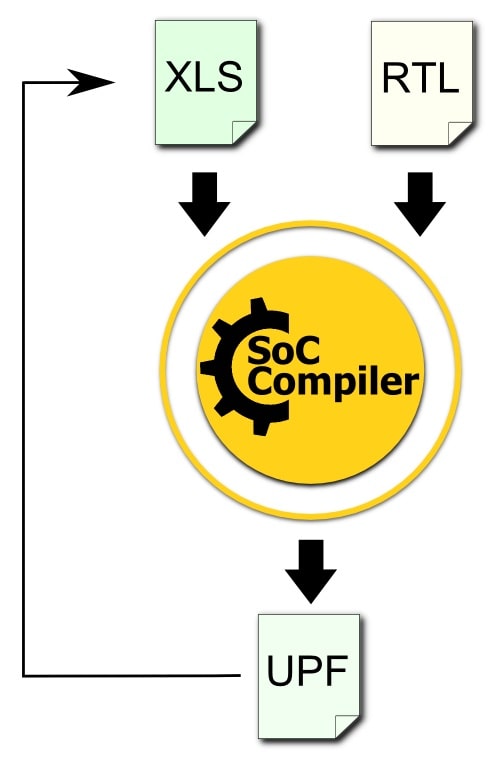

UPF

The Unified Power Format – UPF, started in 2006 and has been used to define the power control intent for chip designs. In the SoC Compiler tool flow it will create a UPF file that is correct-by-construction, allowing you to validate power intent consistency.

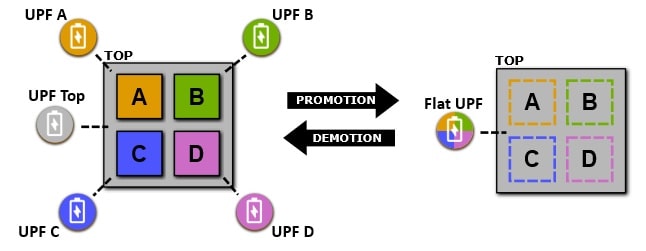

The new ability added to SoC Compiler for UPF are:

- Promotion – merge power-intent into higher scope

- Demotion – split or propagate power-intent into lower scope

So it’s easy to restructure your IP, then automatically update the UPF files without resorting to manual and tedious editing.

DFT

To reach the highest test coverage goals, and reduce test time, an ATPG tool can propose a list of Test Points, but the problem is that this happens too late in the design flow, after logic synthesis. A new feature in SoC Compiler is for Test Point exploration, where you define the target coverage, type and number of Test Points, and the location of inserted Test Points, then it creates a new design with Test Points added. This allows you to quickly trade-off the number of Test Points to be used vs coverage.

DAC 2022

When visiting San Francisco from July 10-14 at Moscone Center, West Hall, make sure to stop by the Defacto Booth on the first floor, #1543. Ask to see Bastien Gratréaux or Chouki Aktouf.

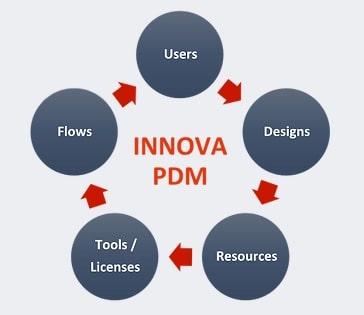

Innova Advanced Technologies

A new spin-off from Defacto was founded in November 2020, Innova Advanced Technologies, and that company is focused on a design flow, resource and project management portal. This approach replaces in-house tools to manage design flows.

Summary

SoC design with IP reuse is a big challenge, because of the scale and complexity involved, so using the most efficient EDA tool flow makes economic sense. Defacto Technologies has been addressing this challenge through automation in SoC Compiler using standard formats like IP-XACT, UPF and RTL. The new features with each release are designed to save your precious SoC design time by eliminating manual tasks.

Related Blogs

- Working with the Unified Power Format

- Webinar – How to manage IP-XACT complexity in conjunction with RTL implementation flow

- WEBINAR: What Makes SoC Compiler The Shortest Path from SoC Design Specification to Logic Synthesis?

- Small EDA Company with Something New: SoC Compiler

- CEO Interview: Dr. Chouki Aktouf of Defacto

Comments

There are no comments yet.

You must register or log in to view/post comments.