Traditionally ATPG (Automatic Test Pattern Generation) and BIST (Built-In-Self-Test) are the two approaches for testing the whole semiconductor design squeezed on an IC; ATPG requires external test equipment and test vectors to test targeted faults, BIST circuit is implemented on chip along with the functional logic of IC. As is evident from the ‘external and internal to an IC’ approaches, both have unique advantages and limitations.

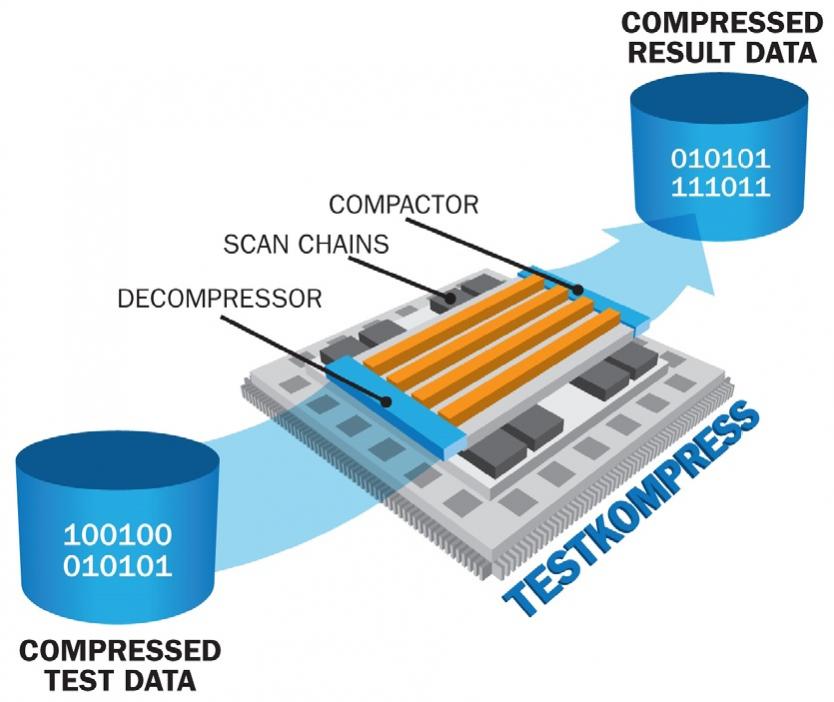

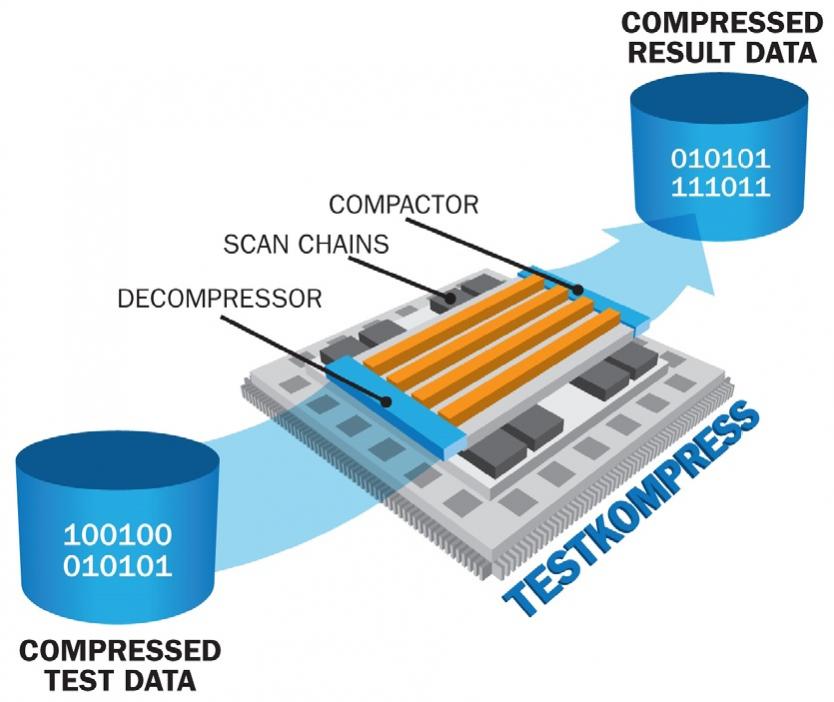

By using ATPG any digital design chip can be tested with high quality covering wide variety of defect detection and fault models such as stuck-at, transition, bridge, path-delay, small-delay etc. However, it requires large number of test patterns to get high fault coverage. And 99% and more fault coverage is a norm in today’s complex chip design to sustain required quality. Therefore, compressed test data is stored in the tester and is applied to the chip scan chains put between a de-compressor and a compactor, thus speeding up the test and requiring lesser tester memory.

By using ATPG any digital design chip can be tested with high quality covering wide variety of defect detection and fault models such as stuck-at, transition, bridge, path-delay, small-delay etc. However, it requires large number of test patterns to get high fault coverage. And 99% and more fault coverage is a norm in today’s complex chip design to sustain required quality. Therefore, compressed test data is stored in the tester and is applied to the chip scan chains put between a de-compressor and a compactor, thus speeding up the test and requiring lesser tester memory.

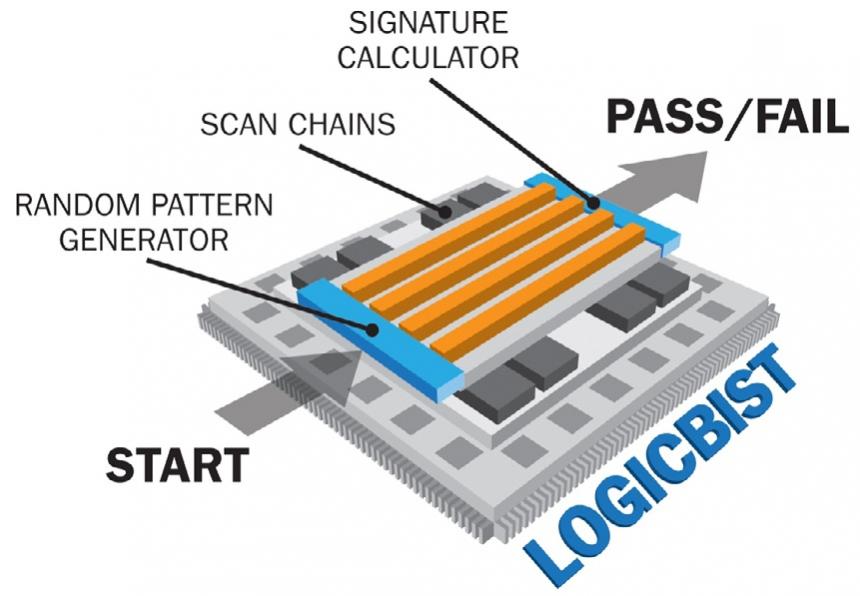

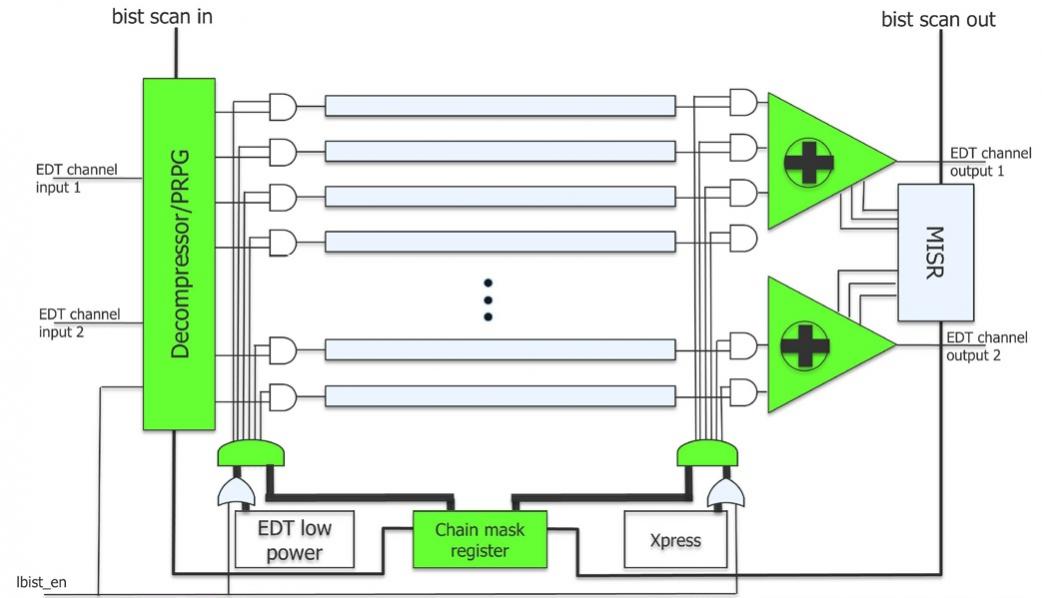

On the other hand logic BIST can be used in any environment (without the need of any tester) for designs that need re-test on system. This proves to be very important for system self-test in critical applications such as satellite, automobile or flight control systems. It’s a very practical approach for plug-and-play design support with short test time, provided the design is not pseudo-random resistant. In an internal arrangement, a pseudo-random pattern generator (PRPG) generates test patterns which pass through the scan chains and the responses are collected in a multiple input signature register (MISR) that determines the pass or fail by comparing to the expected signature. This approach has less coverage on faults that need special targeting unlike ATPG.

Again, in ATPG, a FF capturing a wrong value (due to design issue) can be masked at a mild loss of fault coverage. But in logic BIST, entire chain between the PRPG and MISR will need masking for such cases. Logic BIST cannot tolerate any unknown value (due to any non-scan instance) whereas ATPG can ignore any unknown value at the tester. That means a higher design impact in case of BIST insertion than in ATPG compression.

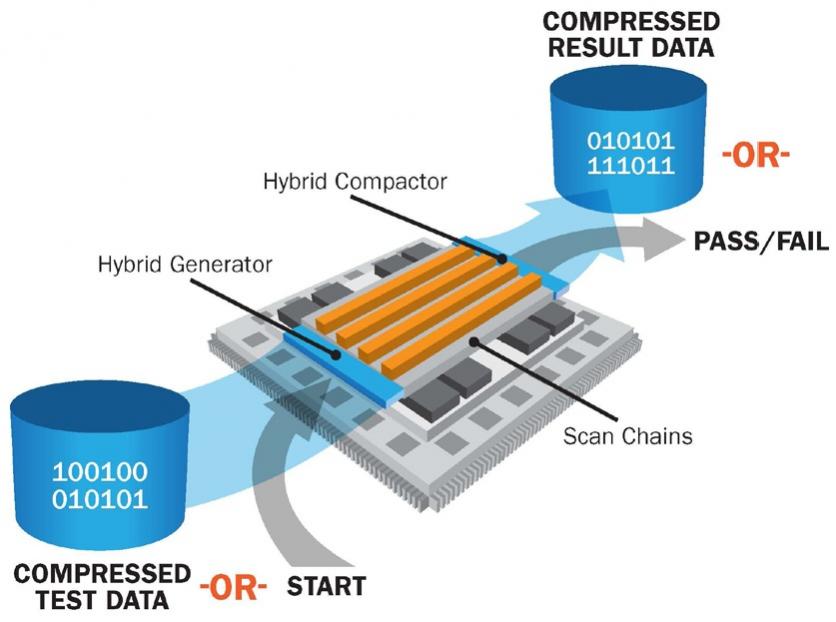

So what should be the best strategy to attain maximum coverage in shortest possible test time? As we can see, ATPG and BIST can be used to complement each other, and both offering more common features these days, Mentorhas exploited these into a hybrid approach by combining the logic from embedded compression ATPG and logic BIST (LBIST).

[Hybrid shared test logic with top-level LBIST controller to manage clocking and sequencing of LBIST tests]

Most common logic of the two test methodology is merged, thus saving in area. Compression ATPG and LBIST are shared within each design block and there is an additional LBIST controller at the top level. In this approach, ATPG needs to target only those faults that are not already detected by LBIST, thus saving test time significantly.

This hybrid approach which can be used in top-down as well as bottom-up design flow, saves hardware cost as well as test time and provides highest fault coverage. Also, in case of bottom-up flow Mentor’s Tessent TestKompress can re-use the patterns previously generated at the core level, thus saving in test pattern generation time.

EDA vendors such as Mentor provide tools to re-use logic between embedded compression ATPG and LBIST. A whitepaperat Mentor’s website provides a great level of detail about ATPG, LBIST and the hybrid approach of test strategies. Interesting read!!

More Articles by Pawan Fangaria…..

lang: en_US

Share this post via:

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?