Over the years DRC tools have done an admirable job of keeping pace with the huge growth of IC design size. Yet, DRC runs for sign off on the full design using foundry rule decks take many hours to complete. These long run times are acceptable for final sign off, but there are many situations where DRC results are needed quickly when small changes are being made to the design to fix late stage issues. Siemens EDA in conjunction with MaxLinear has written a white paper that shows how Calibre RealTime Digital in-design DRC can provide DRC results quickly when small changes have been made in the design. Quicker DRC turnaround for localized changes can speed up iterative error fixing that is often needed to reach tapeout.

In the white paper titled “MaxLinear and Calibre RealTime Digital: Faster signoff DRC convergence plus design optimization for manufacturability “ MaxLinear and Siemens talk about the circumstances where having the ability to run DRC on a small region of a design with the full foundry rule deck can save many hours and painful slow iterations.

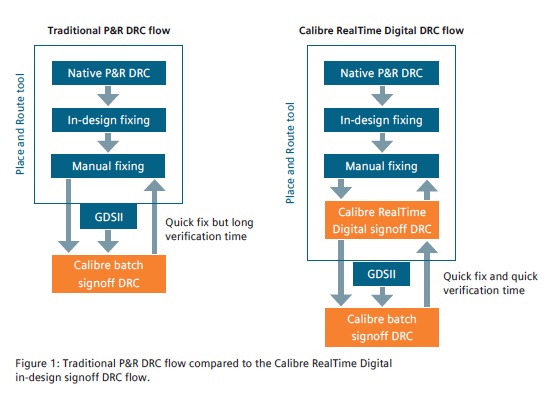

Modern P&R tools do an excellent job of producing DRC correct layout. However, there are always instances where the sources of violations are more complex and are missed during P&R. These usually require a manual fix taking into consideration complex design rules. During these manual fixes there is also the likelihood that new errors may be introduced. Siemens presents information from MaxLinear in the white paper that highlights how Calibre RealTime Digital interfaced with their P&R tool allows them to quickly implement and validate manual fixes. The alternative is to perform a full DRC run just to see if changes in a small area are correct.

MaxLinear makes chips with analog and digital blocks. The analog blocks require fewer metal layers, so to reduce manufacturing cost they seek to reduce routing layers in the full design. This creates routing density issues, which often conflict with maintaining a high DFM ranking. Single-cut vias use the least space but contribute to a low DFM ranking. When push comes to shove MaxLinear designers can manually switch via types to deal with routability versus DFM tradeoffs. But these need to be followed up with a comprehensive DRC to check for things like multi-patterning violations. Calibre RealTime Digital lets designers swap via types and then quickly see if any DRC errors exist.

Vias are not the only problem that can lead to DRC issues that require time and effort to resolve. The white paper describes several situations where manual work is required and the only way to finally resolve these issues is to get a clean DRC run. One of these situations that happens late in the process is when re-tapeout (RTO) checks are needed to ensure ECOs are compatible with existing masks. RTO rules are by nature more restrictive than the original DRC rules.

The white paper also touches on electromigration issues that can be caused by the use of improper vias. Here again Calibre ReatTime Digital was instrumental for MaxLinear in implementing DRC correct via replacement. Taken all together there are many circumstances that require DRC checks after small changes are made to correct functional or manufacturability issues in a design. Having the ability to get immediate results, instead of waiting for a day or longer turnaround on full DRC run, can shave days or weeks off of a project. It’s not good to find surprises after a big DRC run. Siemens Calibre RealTime Digital interface to P&R tools seems to be an ideal fit for this. This Siemens white paper can be found on the Siemens EDA website.

Also Read:

Heterogeneous Chiplets Design and Integration

Heterogeneous Chiplets Design and Integration

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.