One area of iteration that is becoming more problematic is between floorplanning and synthesis. So much of timing is driven by placement that fixing timing and even power often involves not just re-synthesis and re-placement but alterations to the floorplan. The Achilles heel of existing methods is that floorplanning tools are forced to use a “fixed netlist” as a starting point, which forces them to go through a continuous iteration loop with synthesis teams to optimize their floorplan, make incrementatl physical changes then optimize with synthesis.

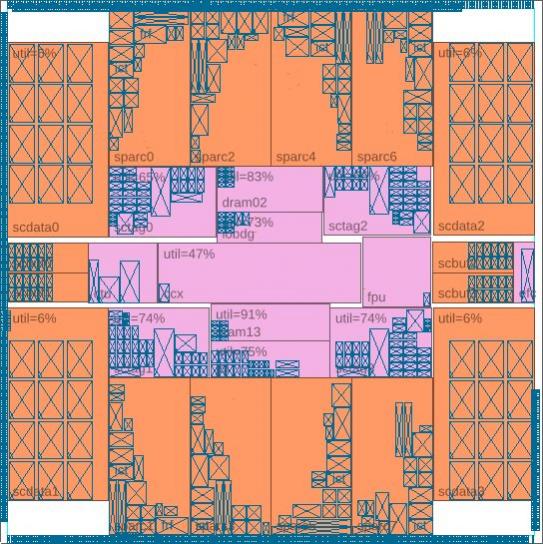

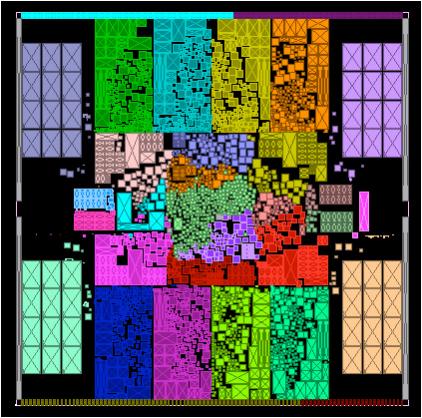

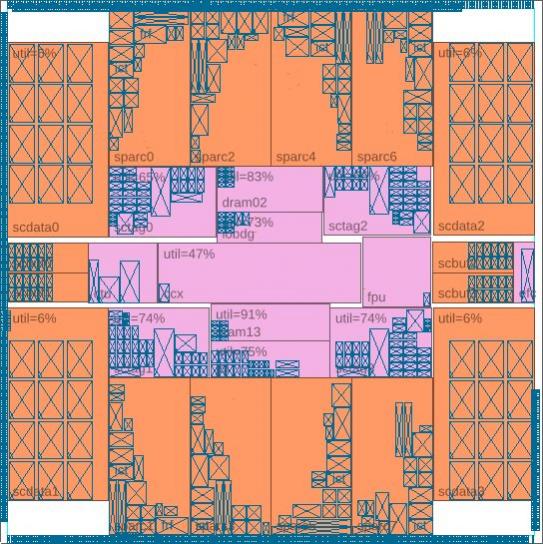

Oasys RealTime can plug into and complement existing flows – front end team generates an initial floorplan which they then feed forward as initial guidance to the physical design teams. The front end design team can create a floorplan directly from the RTL that is aware of the design’s dataflow and also meets all the constraints for timing, power, area and routing congestion. It only takes 2-3 days to generate and is about 90% the same as the final production floorplan and thus forms a good starting point for physical design. Compared to current methods RealTime saves about a month out of the schedule.

There are actually two different ways to use RealTime to feed a design forward into physical design, depending on whether the physical design team intends to re-synthesize the design completely using a different synthesis tool. There are many reasons for doing this, ranging from having a huge pool of licenses, training, corporate standards and so on.

If a different synthesis tool is being used, then the floorplan is fed forward from the front end team as a DEF file. The design is then synthesized with the traditional synthesis tool and then physical design and signoff occurs as normal.

The alternative is to use RealTime as “the” synthesis tool. In this case the front end team produce more than a floorplan, they produce a detailed placement DEF and a synthesized netlist. This allows the user to get the best possible starting point for the physical design team. The placement is not completely perfect since certain aspects of physical design such as detailed power routing are not taken into account. An additional benefit of this approach is that typically, in addition to synthesis being fast due to RealTime’s RTL-based approach, physical design is often faster since the design is already very close the final result (the routing and signoff still has to be done of course).

Floorplan Compiler can generate an initial floorplan automatically from the RTL, including taking into account blocks such as memories. The advanced editing tools make it easy to take that initially created floorplan, make changes and then iterate getting better versions multiple times per day. One of the most time consuming tasks, and one of the most critical, in SoC design is getting a good quality floorplan.RealTime reduces the time required for this task from a typical 4-6 weeks down to a few days, saving around a month.

More details on Floorplan Compiler are available here.

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era