Introduction of 2.5D and 3D multi-die based products are helping extend the boundaries of Moore’s Law, overcoming limitations in speed and capacity for high-end computational tasks. In spite of its critical function within the 3DIC paradigm, the interposer die’s role and related challenges are often neither fully comprehended… Read More

Tag: floorplanning

Ensuring 3D IC Semiconductor Reliability: Challenges and Solutions for Successful Integration

One of the most promising advancements in the semiconductor field is the development of 3D Integrated Circuits (3D ICs). 3D ICs enable companies to partition semiconductor designs and seamlessly integrate silicon Intellectual Property (IP) at the most suitable process nodes and processes. This strategic partitioning yields… Read More

Cadence is Making Floorplanning Easier by Changing the Rules

SoC designs are getting more complex, resulting in a higher level of difficulty to get anything done. This trend is well-known. What I want to focus on here is how to deal with the issue of complexity. There are many approaches to taming this problem — faster algorithms for one, and improved algorithm efficiency or the ability to run… Read More

Apogee Pipelining in Real Time

Pipelining exploits parallelism of sub-processes with intent to achieve a performance gain that otherwise is not possible. A design technique initially embraced at the CPU micro-architectural level, it is achieved by overlapping the execution of previously segregated processor instructions –commonly referred … Read More

What NoCs with virtual channels really do for SoCs

Most of us understand the basic concept of a virtual channel: mapping multiple channels of traffic, possibly of mixed priority, to a single physical link. Where priority varies, quality of service (QoS) settings can help ensure higher priority traffic flows unimpeded. SoC designers can capture the benefits of virtual channels… Read More

Floorplanning Merged With Synthesis

One area of iteration that is becoming more problematic is between floorplanning and synthesis. So much of timing is driven by placement that fixing timing and even power often involves not just re-synthesis and re-placement but alterations to the floorplan. The Achilles heel of existing methods is that floorplanning tools … Read More

Cadence Digital Flow

Cadence has a series of webinars about their digital flow, focused on 28nm design. It is easy for all of us in the EDA ecosystem to assume that everyone is already doing 20/22nm design, if not 14nm already. But in fact most designs are still being done at 45nm and 65nm; 28nm is still a big challenging step.

One of the tools in the Cadence… Read More

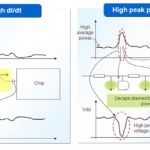

Semiconductor RTL Power Analysis: the sweet spot

Power has become the strongest driver of semiconductor design today, more important than area, more important than timing. Whether the device is handheld, like a wireless phone, or tethered, like a router, complex power and energy requirements must be met. Shrinking geometries continue to impose new challenges as power management… Read More