Each year Calypto runs a survey of end-users. This year’s survey and report has two parts, power reduction and high level synthesis (HLS).

The topics covered are:

- survey methodology and demographics

- top methods used to reduce power

- engineering time spent on specfiic RTL tasks to reduce power

- plans to deploy RTL power reduction tools in 2013

- methods to verify HLS output RTL

- important technologies to implement with HLS

- summary

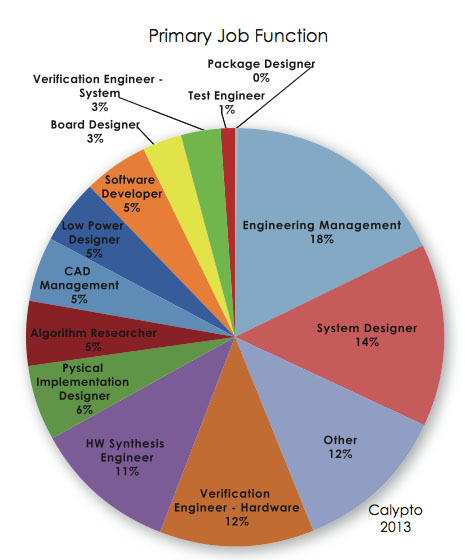

The above pie-chart shows the detailed breakdown. The primary job functions specified were engineering and CAD management (23%), system designer (14%), verification engineer – hardware (12%), and hardware synthesis engineers (11%).

I’m not going to go into the whole report here, you can download it and read the whole thing. But I’ll pick out a couple of interesting charts.

The first one shows the popularity of the main means of power reduction. This is at the RTL level so some techniques for power reduction are applicable only at other stages in the design process.

- Top is sequential power gating (such as is done by PowerPro and its competitors).

- Power gating, which is powering down blocks that are completely unused, such as the transmit/receive logic in a cellphone when there is no call taking place

- Third is combinational clock gating. I think this is so universal that people don’t always realize they are using it since synthesis does it semi-automatically, so I’m surprised it isn’t #1. It usually is in this sort of survey.

- Next is dynamic voltage and frequency scaling (DVFS) which is surprisingly high to me. It is a difficult technique to use requiring careful tuning of how fast and in what order the frequencies and voltages are changed. It is used in high end microprocessors but I’ve not really heard of it in other parts of big SoCs

- Next is multi V[SUB]th[/SUB], again a relatively low score if it covers using multi V[SUB]th[/SUB] libraries. RTL synthesis does this automatically so many people may be unaware they are doing this even when they are.

- Resource sharing, memory gating and data gating bring up the rear.

Interestingly, the chart above shows which techniques are used to verifying high level synthesis RTL against its original input doesn’t have a lot of people using sequential formal verification, which I find a bit surprising. FPGA prototyping seems a poor substitute for formal techniques. After all, for RTL synthesis we pretty much use formal techniques rather than simulation these days. Anyway, since Calypto has the only sequential formal verification tool on the market today, that is a potentially high growth opportunity.

So in summary, SoC, IC, and FPGA design professionals completed a blind, anonymous survey online.

- The average time spent on various RTL power tasks was: 20 percent on automated optimization, 20 percent on guided/manual power reduction, and 17 percent RTL power analysis.

- The combined total organizational involvement with using, implementing, or evaluating RTL power reduction technology is close to two-thirds. Almost a quarter of respondents said their organization had already implemented RTL power reduction tools.

- More than three-quarters of respondents used HLS. The top method for verifying the RTL output was FPGA prototyping. There was a range of usage among directed tests, assertion-based, constrained random, hardware emulation, and C-to-RTL formal.

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era