This year for DAC, Calypto has assembled an impressive lineup of customer presentation, suite sessions and Designer Tracks. To start with customer presentation, Steve Kommrusch, Fellow Design Engineer from AMD will be giving a talk in the Calypto Suite on AMD’s methodology for low power and will show how AMD was able to get further 20% power reduction on a SoC that was already optimized for low power. AMD’s methodology for low power is centered on the notion of efficient clock gating. In this private suite presentation, Steve Kommrusch from AMD will discuss AMD’s methodology for reducing power on the Jaguar SoC and will show how AMD used PowerPro to improve clock-gating efficiency. Steve will also share the results and advantages of doing power analysis and optimization at the RTL stage rather than waiting until post-gate synthesis.

Another customer presentation in the suite is from Renesas. In this private presentation Shintaro Imamura-san of Renesas, will describe how they were able to cut down verification time by using C to C and HLS formal equivalency flow using Calypto’s SLEC product. This presentation will be given in English and Japanese at two different times.

As some of you may know, Calypto has been running a webinar series that has been very successful. What I like about Calypto’s webinar series is that it is truly a technical tutorial and without any marketing or product pitch. Calypto has scheduled two of its most popular webinars in the suite session.

The first one is How to Use Deep Sequential Analysis to Minimize Power. In this 50 minute tutorial, Calypto will review the requirements for a comprehensive methodology to reduce power at the RTL. They will cover basic, yet important concepts; such as how to best set up your environment to accurately measure power. The tutorial will cover more advanced topics—such as how to analyze the RTL for wasted power—and show optimization techniques to reduce power on real designs. The latest sequential analysis techniques will be described; including stability-based and observability-based sequential clock gating for maximum power optimization.

The other one is A Practical Comparison between C++ and SystemC for High Level Synthesis. This 50 minute tutorial will provide a practical overview of the differences between the two most common ESL hardware description languages. The tutorial will show side-by-side coding examples for basic hardware concepts; such as, hierarchy, IO, numerical precision, and timing. As the only company to support both SystemC and C++ for synthesis with the industry’s most successful HLS tool (Catapult), Calypto is uniquely placed to discuss the differences between the two languages.

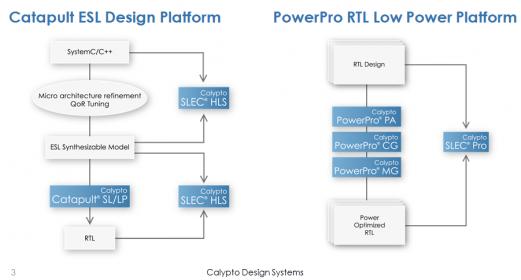

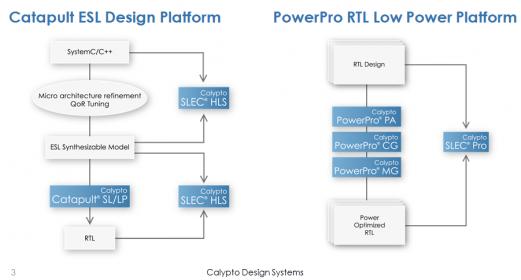

In addition to these special suite session, there are number of suite sessions on Calypto’s three product lines: Catapult, which is a high level synthesis tool that takes C++ or SystemC and synthesizes it into Verilog or VHDL RTL. PowerPro is industry’s only RTL power analysis and optimization tool that incorporates Calypto’s patented deep sequential analysis technology for best power optimization. SLEC is industry’s only production proven sequential equivalence checker.

Calyptp will also be showing Catapult LP. Catapult LP embeds Calypto’s unique PowerPro® technology “under the hood” to seamlessly produce the lowest power RTL by optimizing designs at the architectural and register transfer levels, where 80% of power decisions are made. Catapult LP enables designers to explore different hardware architectures and measure the power, performance, and area (PPA) of each solution. The net result is an ability to perform architectural refinement from an abstract C++ or SystemC model and deliver closed loop PPA optimization during high-level synthesis. Catapult LP goes beyond the architecture level by leveraging Calypto’s patented sequential analysis technology to deliver automatic fine-grain clock gating. In this session we will show how to design for the lowest power hardware by first optimizing the architecture and then maximizing clock gating efficiency.

In addition to these suite sessions which are listed on the Calypto website and users can sign up for them, there are some private sessions which are not listed and is by invitation only. These sessions are about new products and future roadmap. To find out more about these sessions contact your Calypto account manager.

There are also two Designer Tracks that talk about Calypto’s PowerPro product. In the first one on Tuesday, Udupi Harisharan, of Cisco Systems will discuss Practical Consideration in a Sequential Power Optimization Flow. In the Wednesday Designer Track session, Steve Kommrusch of AMD will discuss how AMD’s Power Regression Methodology Reduces Dynamic Power by 20%.

There is also an Insight presentation where Calypto’s Bryan Bowyer will talk about Reducing Design and Debug Time with Synthesizable TLM

To get more details and sign up for these presentations, visit http://calypto.com/en/events

lang: en_US

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center