Cavium designs some very complex SoCs containing multiple ARM or MIPS cores at 32 and 64 bit. This complexity leads to major challenges in validating the overall chip architecture to ensure that their designs will meet the requirements of their customers once they are completed, with performance as high as 100Gbps.

Cavium designs some very complex SoCs containing multiple ARM or MIPS cores at 32 and 64 bit. This complexity leads to major challenges in validating the overall chip architecture to ensure that their designs will meet the requirements of their customers once they are completed, with performance as high as 100Gbps.

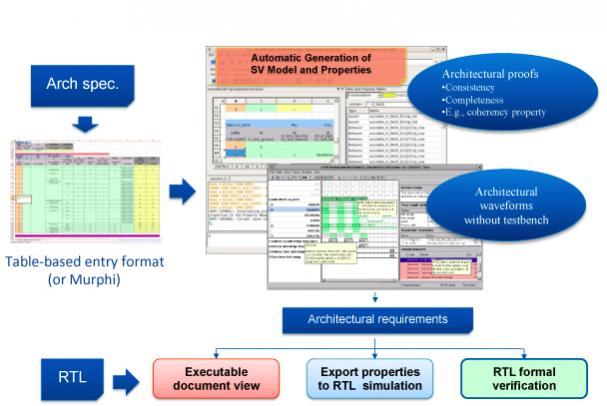

Cavium have decided to use Japer’s JasperGold Architectural Modeling App to allow their architects to better specify, model and verify the complex behavior of these bleeding edge designs. I’ve written before on how ARM has been using Jasper’s architectural modeling to verify their own cache protocols (and, indeed, found some corner-case errors that all their other verification had missed). Cavium’s multi-core, multi-processor chips for sure have very complex interconnection protocols between the processors and memories.

The JasperGold Architectural Modeling App provides an easy and well-defined methodology for an efficient modeling and verification of complex protocols. Jasper’s Modeling App models a large part of the protocol much faster and with less effort compared to other modeling and validation methods. It captures protocol specification knowledge at the architectural level; performs exhaustive verification of complex protocols against the specification; creates a golden reference model that can be used in verifying the RTL implementation of the protocol; and automates protocol-related property generation and debugging aids.

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea