The industry plans to use 193nm light at the 20nm, 14nm, and 10nm nodes. Amazing, no? There is no magic wand; scientists have been hard at work developing computational lithography techniques that can pull one more rabbit out of the optical lithography hat.

The industry plans to use 193nm light at the 20nm, 14nm, and 10nm nodes. Amazing, no? There is no magic wand; scientists have been hard at work developing computational lithography techniques that can pull one more rabbit out of the optical lithography hat.

Tortured metaphors aside, the goal for the post-tapeout flow is the same as always – to compensate for image errors on the wafer due to diffraction or process effects. Resolution enhancement technology (RET) and optical proximity correction (OPC) do this by moving edges and adding sub-resolution shapes to the pattern that will be written to the photomask.

Now, if you are prepared to have your mind blown by new computational lithography techniques, you can sign up for the SPIE Advanced Lithography conference. There is so much going on with computational lithography that I couldn’t start to cover it all here. I’ll introduce two presentations on my list: “Inverse lithography technique (ILT) for advanced CMOS nodes,” by scientists from ST Microelectronics and Mentor Graphics, and “Effective model-based SRAF placement for full-chip 2D layouts” by Mentor Graphics R&D. In both of them, the authors address the problem of lithographic hotspots that can remain after full-chip OPC. Without innovations like those described in these papers, such as the litho quality benefits of free–form SRAF placement, the solution would be to tune your OPC recipe to address each hotspot and maybe, eventually, fix them all. This is not a very good solution.

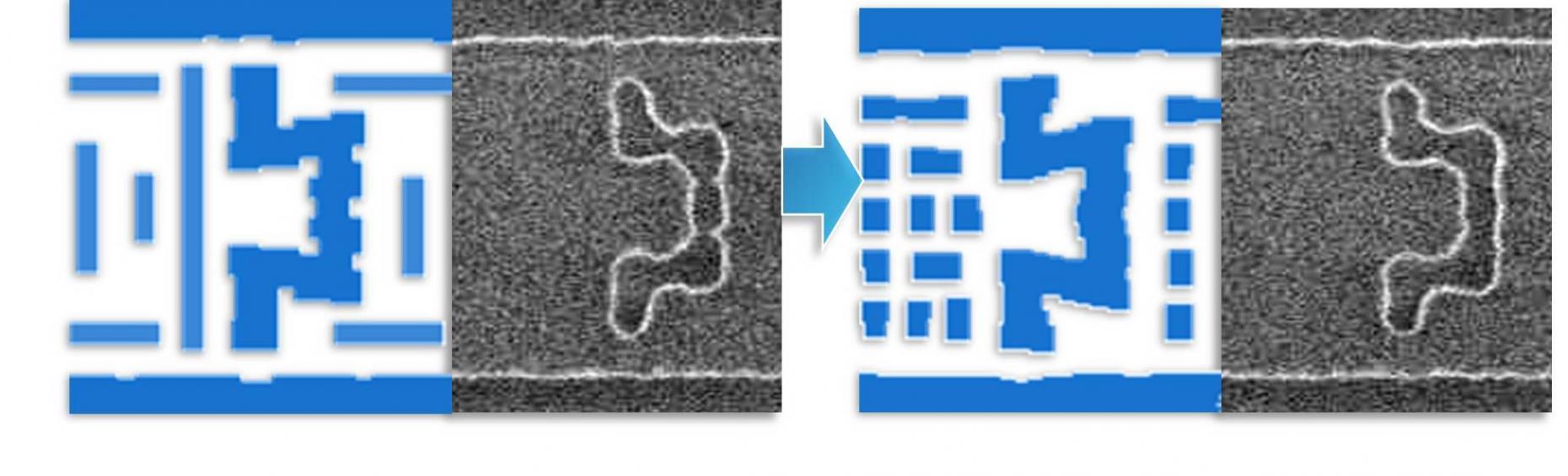

A better way is to use a more aggressive correction approach to solve just the hotspots that remain after traditional OPC/SRAF insertion, and then stitch the result back into the OPC-ed full-chip layout. Inverse lithography technology is so called because rather than moving the fragmented edges of the starting (target) shapes to produce the desired wafer image, it uses a rigorous mathematical approach to solve an inverse problem, thus generating the “ideal output mask (OPC + SRAF) shapes” that will result in the desired image on the wafer. ILT solves an optimization problem, and as such is computationally expensive if applied full-chip. At SPIE, the authors present it as a tool for localized printability enhancement (LPE).

A better way is to use a more aggressive correction approach to solve just the hotspots that remain after traditional OPC/SRAF insertion, and then stitch the result back into the OPC-ed full-chip layout. Inverse lithography technology is so called because rather than moving the fragmented edges of the starting (target) shapes to produce the desired wafer image, it uses a rigorous mathematical approach to solve an inverse problem, thus generating the “ideal output mask (OPC + SRAF) shapes” that will result in the desired image on the wafer. ILT solves an optimization problem, and as such is computationally expensive if applied full-chip. At SPIE, the authors present it as a tool for localized printability enhancement (LPE).

This chart shows their iterative localized printability enhancement flow.

You first perform OPC and SRAF insertion. Verification then gives you a list of hotspots and you apply ILT only to those hotspots. The research presented uses Mentor’s ILT engine (called pxOPC) plus some automation to cut and stitch the repaired areas back into the full layout.

You first perform OPC and SRAF insertion. Verification then gives you a list of hotspots and you apply ILT only to those hotspots. The research presented uses Mentor’s ILT engine (called pxOPC) plus some automation to cut and stitch the repaired areas back into the full layout.

Author Alex Tritchkov of Mentor Graphics told me that with their inverse lithography technology, the OPC and the SRAFs have greater degrees of freedom and can employ non-intuitive but manufacturable shapes. This allows for significant process window improvement for certain critical patterns, which are very hard to achieve with conventional OPC/SRAF insertion.

Tritchkov sees ILT as useful both during R&D when design rules are not established, the OPC/RET recipes are immature, and the test chips are pushing the resolution limits, but also in high-volume production to eliminate rework and reduce cost and risk. Papers 8683-14 and 8683-17 will be presented on Tuesday, 26 February at 3:50pm and 4:50pm, respectively.

Registerfor SPIE today.

Share this post via:

Comments

0 Replies to “Magic? No! It’s Computational Lithography”

You must register or log in to view/post comments.