Firas Mohamed, President and CEO (Ph.D.) of Infiniscale met with me on Monday at DAC to provide an overview of what EDA software they offer to IC designers at the transistor-level.

Vision – analog flow that Monte Carlo simulation is required, which is thousands of circuit simulations, however the higher the sigma the more simulations like 10,000 or 100,000 – way too slow, or too expensive to simulate.

Goal – give you better accuracy at an affordable price.

High sigma analysis, like the idea however not feasible to do millions of simulations.

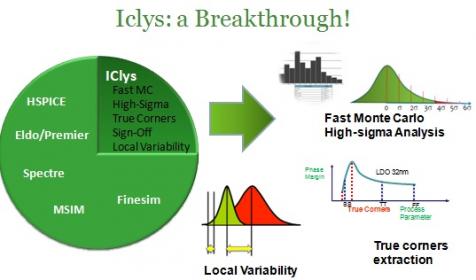

ICLys – provide Monte Carlo analysis in a reasonable amount of run time.

– Input is SPICE netlist and stimulus without knowing about statistics. Ask the simulator to do an equivalent of 50,000 Monte Carlo runs however in fewer runs. Clear report on distributions. No real settings to add to the netlist.

– Tool is incremental, so you can start wtih equivalent of 10,000 runs, then again and ask for 30,000 runs.

– Run fast Monte Carlo or variation analysis. Easy for designer to learn.

– Works with any circuit simulator

– statistics section in library file is used to tell Monte Carlo how to vary.

How can I tell the accuracy of the tool? Run brute force Monte Carlo with Fast MC.

Do you have foundry qualification from TSMC or other foundries?

No, it’s too early for that. Hope that we have qualificaiton later this year.

ST has validated ICLys on its own Design Kits and on IBM Design Kits

Pricing? Distribution in USA through EDATechForce.

3rd party – Mentor and Synopsys now, Cadence under discussion.

Size 13 people in Grenoble. North America using EDATechForce as distributor.

CDA – In France. Leti Semi.

Privately financed.

Technical papers – not yet. Patents applied for.

How are you different from other EDA vendors that offer fast MC? Better performance. Also local variability analysis without capacity limitations.

Summary

Monte Carlo circuit simulation is much needed to predict how an IC design will yield during process variation, so anything that gives your faster Monte Carlo results is much welcomed because it speeds up the design process and helps IC designers create more robust chips. My lingering question is, “How does this approach really compare to that of: Solido, ProPlus, Magma/Synopsys, Cadence and Mentor?”

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!