Engineers are always looking to improve the efficiency of how they work, but don’t want to sacrifice accuracy in the process. This is true in the world of semiconductor process development, where traditional build-and-test cycles are both time and resource intensive. But what if there was a way to do certain steps in a ‘virtual’… Read More

The US Executive Forum 2013

The US Executive Forum hosted by the Global Semiconductor Alliance was held last night at the beautiful Rosewood Sand Hill Hotel in Menlo Park. We all have memorable events in our professional lives and this is one of mine, absolutely. The audience was filled with semiconductor executives from around the world who chatted freely… Read More

Dan Niles: Tapering and the Global Economy

Yesterday was Dan Niles quarterly review that he does for GSA. As always he starts from the big picture of the world economy and works his way to a semiconductor forecast. The focus of this quarter was whether the world economy is strong enough for the US to “taper” and reduce the amount of quantitative easing (aka flooding… Read More

What Does Sports and NoC Have in Common?

As an Oakland Raider season ticket holder I attend as many Raider home games as possible. If you have ever attended a live sporting event at a large stadium, and you travelled by car, you are probably familiar with the traffic problems that occur at the end of the game when everyone wants to leave the stadium parking lot at the same time.… Read More

Using OTP Memories To Keep SoC Power Down

Virtually all SoCs require one-time programmable (OTP) memory. Each SoC is different, of course, but two main uses are large memories for holding boot and programming code and small memories for holding encryption keys and trimming parameters, such as radio tuning information and so on.

There are alternatives to putting an OTP… Read More

Texture decompression is the point for mobile GPUs

In the first post of this series, we named the popular methods for texture compression in OpenGL ES, particularly Imagination Technologies PVRTC on all Apple and many Android mobile devices. Now, let’s explore what texture compression involves, what PVRTC does, and how it differs from other approaches.… Read More

How Do You Do Computational Photography at HD Video Rates?

Increasingly, a GPU is misnamed as a “graphics” processing unit. They are really specialized architecture highly parallel compute engines. You can use these compute engines for graphics, of course, but people are inventive and find ways of using GPUs for other tasks that can take advantage of the highly parallel… Read More

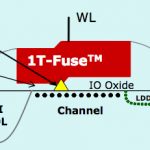

Sidense and TSMC Processes

I’ve written before about the basic capabilities of Sidense’s single transistor one-time programmable memory products (1T-OTP). Just to summarize, it is an anti-fuse device that works by permanently rupturing the gate oxide under the bit-cells storage transistor, something that is obviously irreversible.… Read More

Rapid Yield Optimization at 22nm Through Virtual Fab

Remember? During DAC2013 I talked about a new kind of innovation: A Virtual Fabrication Platform, SEMulator3D, developed by COVENTOR. Now, to my pleasant surprise, there is something to report on the proven results from this platform. IBM, in association with COVENTOR, has successfully implemented a 3D Virtual Fabrication… Read More

OTP Memory to Build Smarter Power Management

All chips have critical power management requirements, often with multiple supply voltages. Digital power management ICs (PMICs) are commonplace to convert unregulated voltages from batteries and noisy power supplies to fully regulated accurate power to keep even the most sensitive chips performing.

Powervation is a company… Read More