Every once in a while, I just scratch my head and wonder just what in the wide, wide world of tech is going on. More than ever, it seems the big barriers to adoption aren’t a lack of technology – instead, barriers come from a system that staunchly defends the old way of doing things, even when the participants are battered, broken, and … Read More

Power Control Moving into Hardware

Sonics have been building networks-on-chips (NoCs) for a long time and have amassed a rich patent portfolio. So being granted a new one isn’t usually deemed press-release-worthy. However, their latest patent on power management is pretty significant. It is patent 8,601,288 titled “Intelligent Power Controller”.

Historically… Read More

If you still think that FDSOI is for low performance IC only…

…then you should read about this benchmark result showing how digital power varies with process corners, for high-speed data networking chip, not exactly the type of IC targeting mid-performance mobile application. Before discussing the benchmark results, we need to have some background about this kind of ASIC chip. Such a … Read More

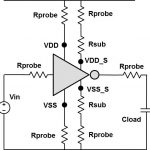

DesignCon 2014 AMS Panel Report

DesignCon 2014 was very crowded! I have not seen the attendance numbers but as the first conference of the New Year it was very encouraging. The strength of the fabless semiconductor ecosystem is collaboration and face-to-face interactions are the most valuable, absolutely.

The session I moderated was on Mixed Signal Design … Read More

iDRM for Complex Layout Searches and IP Protection!

iDRM (integrated design rule manager) from Sage-DA is the world’s first and only design rule compiler. As such it is used to develop and capture design rules graphically, and can be used by non-programmers to quickly capture very complex and shape dependent design rules and immediately generate a check for them. The tool… Read More

Dual Advantage of Intelligent Power Integrity Analysis

Often it is considered safer to be pessimistic in estimating IR-drop to maintain power integrity of semiconductor designs; however that leads to the use of extra buffering and routing resources which may not be necessary. In modern high speed, high density SoCs having multiple blocks, memories, analog IPs with different functionalities… Read More

How Do You Verify a NoC?

Networks-on-chip (NoCs) are very configurable, arguably the most configurable piece of IP that you can put on a chip. The only thing that comes close are highly configurable extensible VLIW processors such as those from Tensilica (Cadence), ARC (Synopsys) and CEVA but Sonics would argue their NoCs are even more flexible. But … Read More

What will drive MEMS to drive I-o-T and I-o-P?

By I-o-P, I mean Internet-of-People- I couldn’t think of anything better than this to describe a technology which becomes your custodian for everything you do; you may consider it as your good companion through life or an invariably controlling spy. This is obvious with the embedded sensor techno-products such as Kolibree, a … Read More

Rekeying the IoT with eMTP

For non-volatile storage in IoT devices, there is technology designed to be reprogrammed many times, and technology designed to be programmed once. The many times mode is for application code, while the once mode is for keying and calibration parameters. We are about to enter the IoT rekeying zone, in between these two extremes.… Read More

Wearables the Big Hit at CES

There were a number of trends discernible at CES this year, one of the big ones being wearables, especially in the medical and fitness areas. I wear a FitBit Flex and I have, but rarely wear, a Pebble Watch that links to my iPhone. I would say that at this point they are promising but are more gimmicks than truly useful. My Fitbit measures… Read More