You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14433

[name] => X-Subscriber

[slug] => x-subscriber

[term_group] => 0

[term_taxonomy_id] => 14433

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 0

[filter] => raw

[cat_ID] => 14433

[category_count] => 0

[category_description] =>

[cat_name] => X-Subscriber

[category_nicename] => x-subscriber

[category_parent] => 0

[is_post] =>

)

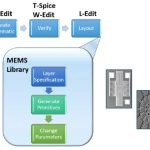

With the industry abuzz about the Apple purchase of a Maxim Integrated fab as a potential R&D facility for MEMS design, it begs the question: is creating a MEMS device that easy?

MEMS technology is approaching the same fork in the road where digital design encountered LSI four decades earlier. … Read More

With every new technology node, there are newer physical effects that need to be taken into account. And every new physical effect brings with itself several new formats to model them. Often a format is also associated with several of its derivatives, sometimes an standard reincarnation of a proprietary format further evolved… Read More

When first interested in computers while I was in junior high school in the early 70’s I remember seeing a core memory board for the first time. It was a seriously large circuit board with a myriad of wires woven across it going through the tiny metal doughnuts that stored the bit values. The computers it went into only had a total of around… Read More

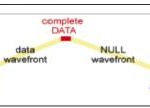

When it comes to predicting SoC performance in the early stages of development, most designers rely on simulation. For network-on-chip (NoC) design, two important factors suggest that simulation by itself may no longer be sufficient in delivering an optimized design.

The first factor is use cases. I think I’ve told the story … Read More

There have always been novel technologies vying to compete with conventional design practices. It is hit or miss on the success of these ideas. In the 90’s I recall speaking to someone who was convinced that they could effectively build computers based on multilevel logic. This, as we know did not pan out. But there have been many … Read More

I have been silently watching STMicroelectronics pursuing FD-SOI technology since quite a few years. FinFET was anyway getting more attention in the semiconductor industry because of several factors involved. But from a technology as well as economic perspective there are many plus points with FD-SOI. I remember my debate,… Read More

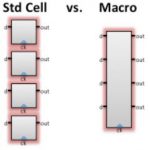

(Two Star Wars™ allusions in one title – eat your heart out George Lucas.) Most of us are comfortable with the idea that you design more or less whatever you want in RTL and let the synthesis tool pick logic gates to implement that functionality. Sure it may need a little guidance here and there but otherwise synthesis is more or less … Read More

You probably have seen many times this graphic showing that the number of IP blocks has exploded, going from a few dozens in SoC designed in 65 nm to 120 if not more for last generation SoC targeting 16FF or 10FF. This graphic is very good at synthesizing the raw IP count, but it doesn’t tell you about another strong trend: more agents … Read More

Software abstraction is a huge benefit of a network-on-chip (NoC), but with flexibility comes the potential for runtime errors. Improper addresses and illegal commands can generate unexpected behavior. Timeouts can occur on congested paths. Security violations can arise from oblivious or malicious access attempts.

Runtime… Read More

One of the most frequently discussed concerns regarding FDSOI adoption is the higher starting wafer cost compared to bulk technology. This discussion was also brought up after my earlier post,… Read More