How do you benchmark a processor? It seems like it should be easy, just run some code and see how fast it is. Traditionally processors were indeed benchmarked by raw performance like GMACS, GFLOPS, memory bandwidth and so on. But in today’s world where systems have become very complex and applications very compute intensive, the… Read More

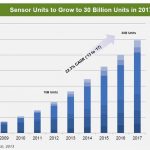

Pre-verified, Integrated Sensor IP Subsystem?

Last year, I said that the launch of ARC based complete sound system IP by Synopsys ring the bell for the opening of a new IP market segment, the “Subsystem IP”. This week, Synopsys has announced the availability of the DesignWare® Sensor IP Subsystem, a complete and integrated hardware and software solution for sensor control applications.… Read More

♫ IMG Sitting on the DOK of the Bay…Closin’ Timin’

Scott Fitzgerald is supposed to have said “the rich are not like other people” to Ernest Hemingway (he didn’t). In the same way, processors are not like other blocks, and not because they have more gates (they don’t). However, special approaches to optimizing processors are important because the clock… Read More

Debugging Verification Constraints

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More

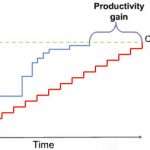

The fixed and the finite: QoR in FPGAs

There is an intriguingly amorphous term in FPGA design circles lately: Quality of Results, or QoR. Fitting a design in an FPGA is just the start – is a design optimal in real estate, throughput, power consumption, and IP reuse? Paradoxically, as FPGAs get bigger and take on bigger signal processing problems, QoR has become a larger… Read More

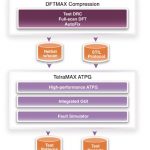

Minimize the Cost of Testing ARM® Processor-based Designs and Other Multicore SoCs

On my first job out of college as an IC design engineer I was surprised to discover that a major cost of chips was in the amount of time spent on the tester before being shipped. That is still true today, so how would you keep your tester time down, test coverage high and with a minimum number of pins when using multiple processors on a single… Read More

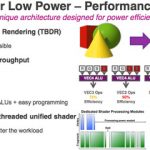

Workload-tuned cores seeing greater interest

Is it possible to design a processor with very high performance and low power consumption? To answer that, embedded illuminati are now focusing on designs tuned to specific workloads – creating a tailored processor that does a few things very efficiently, with nothing extra.… Read More

Aart: Technomic Push-Pull

Aart de Geus gave one of the visionary look to the next 50 years of EDA as a warmup to Stephen Wu’s keynote. EDA is enabling the greatest push-pull ever, part of an exponential change on a scale never before seen.

Technologies seem to go through a 50 year technical push phase (driven by improving the technology) followed by a 50… Read More

Fujitsu, Mediatek, Richtek and Synopsys om Custom IC Design

Synopsys has been acquiring EDA and IP companies at a fast clip over the past few years and it’s often made me wonder how they are going to craft a coherent tool flow for custom IC design. At DACthis year I learned that for schematic capture the winning tool is Custom Designer SE– a relatively new tool, while the IC layout… Read More

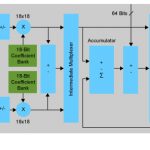

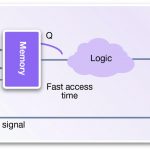

Can we really find a way to speed-up Processor & DSP core designs?

Once upon a time, ASIC designers involved in Processor design, like I was, for the first time in 1987 for Thomson CSF and again in 1994 for Texas Instruments, at that time supporting height (8) ASIC designed by another French company, the Advanced Computer Research Institute (ACRI), had to re-invent the wheel almost every day. When… Read More