One of my favorite traditions at the Design Automation Conference is the Synopsys foundry events (the videos are now available). I learned a long time ago that the foundries are the foundation of the fabless semiconductor ecosystem and your relationships with the foundries can make or break you, absolutely. I also appreciate … Read More

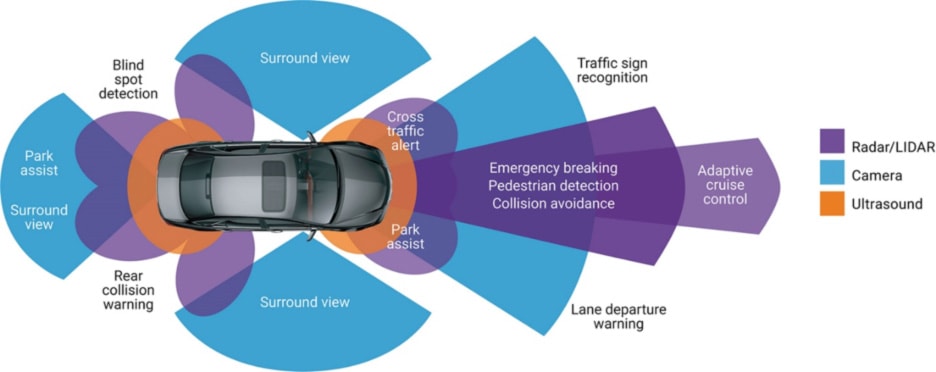

Networking trends for Automotive ADAS Systems

From my restaurant seat today in Lake Oswego, Oregon I watched as an SUV driver backed out and nearly collided with a parked car, so I wanted to wave my arms or start shouting to the driver to warn them about the collision. Cases like this are a daily occurrence to those of us who drive or watch other drivers on the road, so the promises of… Read More

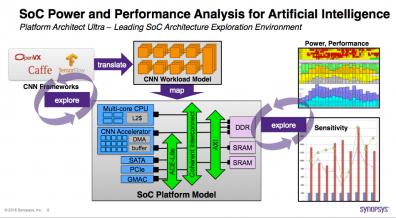

Architecting an ML Design

Discussion on machine learning (ML) and hardware design has been picking up significantly in two fascinating areas: how ML can advance hardware design methods and how hardware design methods can advance building ML systems. Here I’ll talk about the latter, particularly about architecting ML-enabled SoCs. This approach is … Read More

Synopsys Offers First Single-Vendor Comprehensive Photonic IC Design Flow

Synopsys has a long history of being a thought leader and it’s not surprising to see the company jumping into the forefront of new technologies. For decades, I’ve been steeped in electronic IC design and it caught me by surprise to find that Synopsys had been quietly working on filling out their portfolio in the optical design solutions… Read More

AMS Experts Share IC Design Stories at #55DAC

At #55DAC in SFO the first day is always the busiest on the exhibit floor, so Monday by lunch time I was hungry and took a short walk to the Marriott hotel nearby to listen to AMS experts from several companies talk about their EDA tool use, hosted by Synopsys:

- Samsung

- Toshiba Memory Corp.

- NVIDIA

- Seagate

- Numem

- Esperanto

Automotive is setting the goalposts for next generation designs

Automotive applications are having a tremendous influence on semiconductor design. This influence is coming from innovations in cloud computing, artificial intelligence, communications, sensors that all serve the requirements of the automotive market. It should come as no surprise that ADAS and autonomous driving are … Read More

Accelerated Verification with Synopsys

At DAC 2018, Synopsys held a lunch panel discussing verification challenges faced by the industry leaders, their adopted approaches and the overall verification technology trends. This panel of industry experts from Intel, AMD, Samsung, STM and Qualcomm also shared their viewpoints on what drives the SoC complexity and how… Read More

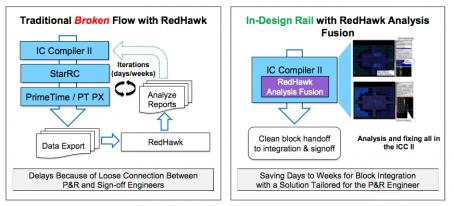

Integrity, Reliability Shift Left with ICC

There is a nice serendipity in discovering that two companies I cover are working together. Good for them naturally but makes my job easier because I already have a good idea about the benefits of the partnership. Synopsys and ANSYS announced a collaboration at DAC 2017 for accelerating design optimization for HPS, mobile and automotive.… Read More

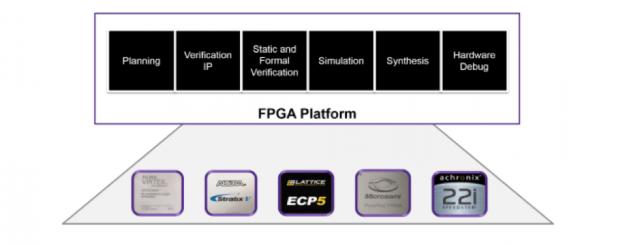

When FPGA Design Looks More Like ASIC Design

I am sure there are many FPGA designers who are quite content to rely on hardware vendor tools to define, check, implement and burn their FPGAs, and who prefer to test in-system to validate functionality. But that approach is unlikely to work when you’re building on the big SoC platforms – Zynq, Arria and even the big non-SoC devices.… Read More

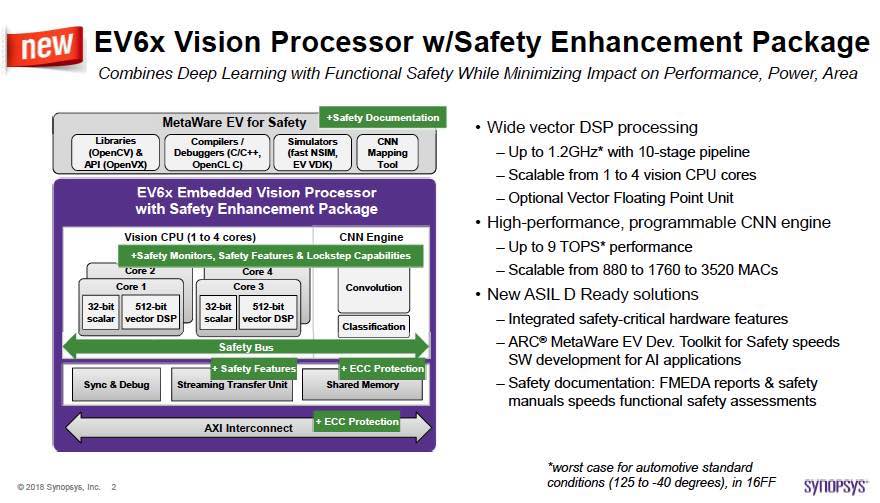

ISO 26262 First – ASIL-D Ready Vision Processor IP Available

Synopsys made a pretty major announcement regarding their new ASIL-B,C and D ready embedded vision processor IP. This matters because you cannot bolt on the design elements and features needed to achieve these ASIL levels later, and this IP is absolutely necessary for ADAS systems and other critical safety systems in automobiles.… Read More