IEDM was buzzing with many presentations about the newest gate-all-around transistor. Both Intel and TSMC announced processes based on nanosheet technology. This significant process innovation allows the fabrication of silicon RibbonFET CMOS devices, which promise to open a new era of transistor scaling, keeping Moore’s… Read More

Intel – Everyone’s Favourite Second Source?

A response to Daniel Nenni’s “What’s Wrong with Intel?” article, which invited alternative views.

At the risk of calling down the forecast universal opprobrium, I’m going to disagree with Dan’s take on the centrality of Intel.

I don’t agree that Intel is too big/important to fail or that the US can’t succeed in semiconductors without… Read More

An Invited Talk at IEDM: Intel’s Mr. Transistor Presents The Incredible Shrinking Transistor – Shattering Perceived Barriers and Forging Ahead

IEDM turned 70 last week. This was cause for much celebration in the form of special events. One such event was a special invited paper on Tuesday afternoon from Intel’s Tahir Ghani, or Mr. Transistor as he is known. Tahir has been driving innovation at Intel for a very long time. He is an eyewitness to the incredible impact of the Moore’s… Read More

What is Wrong with Intel?

One of the most popular topics on the SemiWiki forum is Intel, which I understand. Many of us grew up with Intel, some of us have worked there, and I can say that the vast majority of us want Intel to succeed. The latest Intel PR debacle is the abrupt departure of CEO Pat Gelsinger. To me this confirms the answer to the question, “What is … Read More

Podcast EP265: The History of Moore’s Law and What Lies Ahead with Intel’s Mr. Transistor

Dan is joined by Dr. Tahir Ghani, Intel senior fellow and director of process pathfinding in Intel’s Technology Research Group. Tahir has a 30-year career at Intel working on many innovations, including strained silicon, high-K metal gate devices, FinFETs, RibbonFETs, and backside power delivery (BSPD), among others. He has… Read More

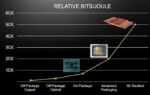

Intel and Cadence Collaborate to Advance the All-Important UCIe Standard

The Universal Chiplet Interconnect Express™ (UCIe™) 1.0 specification was announced in early 2022 and a UCIe 1.1 update was released on August 8, 2023. This open standard facilitates the heterogeneous integration of die-to-die link interconnects within the same package. This is a fancy way of saying the standard opens the door… Read More

3D IC Design Ecosystem Panel at #61DAC

At #61DAC our very own Daniel Nenni from SemiWiki moderated an informative panel discussion on the topic of 3D IC Design Ecosystem. Panelists included: Deepak Kulkarni – AMD, Lalitha Immaneni – Intel Foundry, Trupti Deshpande – Qualcomm, Rob Aitken – CHIPS, Puneet Gupta – UCLA, Dragomir Milojevic – imec. Each panelist had a brief… Read More

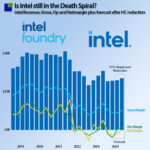

Intel’s Death Spiral Took Another Turn

Does this justify the widespread Intel bashing?

The latest Intel earnings release was another sharp and deeper turn into the company’s death spiral. On the surface, it is just a whole load of bad news, and the web has been vibrating with Intel bashing since the release.

So what are the facts?

From a revenue perspective, Intel was inside… Read More

Podcast EP238: Intel Capital’s Focus on Improving the Future of Semiconductors with Jennifer Ard

Dan is joined by Jennifer Ard, Intel Capital Managing Director and Head of Investment Operations. In her role, Jen is responsible for managing Intel Capital’s investment-related operations. Additionally, she is primarily focused on investing in silicon-related companies and has been involved in multiple deals including… Read More

Intel’s Gary Patton Shows the Way to a Systems Foundry #61DAC

#61DAC was buzzing this year with talk of AI and multi-die, heterogeneous design. The promise of making 2.5/3D design and a chiplet ecosystem mainstream reality was the focus of a lot of the panels and presentations at the conference. AI is certainly a driver for this new design style, but the conversation was broader than just AI,… Read More