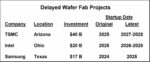

U.S. President Biden announced on Wednesday an agreement to provide Intel with $8.5 billion in direct funding and $11 billion in loans under the CHIPS and Science Act. Intel will use the funding for wafer fabs in Arizona, Ohio, New Mexico, and Oregon. As reported in our December 2023 newsletter, the CHIPS Act provides a total of $52.7… Read More

Simulating the Whole Car with Multi-Domain Simulation

Next significant automotive blog in a string I will be posting (see here for the previous blog).

In the semiconductor world, mixed simulation means mixing logic sim, circuit sim, virtual sim (for software running on the hardware we are designing) along with emulation and FPGA prototyping. While that span may seem all-encompassing,… Read More

Can Correlation Between Simulation and Measurement be Achieved for Advanced Designs?

“What you simulate is what you get.” This is the holy grail of many forms of system design. Achieving a high level of accuracy between predicted and actual performance can cut design time way down, resulting in better cost margins, time to market and overall success rates. Achieving a high degree of confidence in predicted performance… Read More

CEO Interview: Patrick T. Bowen of Neurophos

Patrick is an entrepreneur with a background in physics and metamaterials. Patrick sets the vision for the future of the Neurophos architecture and directs his team in research and development, particularly in metamaterials design. He has a Master’s degree in Micro-Nano systems from ETH Zurich and PhD in Electrical Engineering… Read More

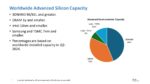

No! TSMC does not Make 90% of Advanced Silicon

Throughout the debate on fab incentives and the Chips Act I keep seeing comments like; TSMC makes >90% of all advanced silicon, or sometimes Taiwan make >90% of all advanced silicon. This kind of ill-defined and grossly inaccurate statement drives me crazy. I just saw someone make that same claim in the SemiWiki forums and… Read More

How Sarcina Technology Makes Advanced Semiconductor Package Design Easier

For a long time, package engineering was part of the cleanup crew for chip design. The glory was all around the design of advance monolithic chips on the latest technology node. Once the design was done, the package/test team would take the design over the finish line, adding the required I/O specs, lead frame, load board and test … Read More

SPIE Let there be Light! High NA Kickoff! Samsung Slows? “Rapid” Decline?

– High NA EUV’s coming out party – “Dawn” of the Angstrom Era

– Well attended, positive vibes, not much new but good progress

– Concerns about Samsung slowing spend while Intel accelerates

– KLA reticle inspection quandary – Risky business in China

SPIE was a High-NA

… Read MoreCEO Interview: Larry Zu of Sarcina Technology

Larry has grown Sarcina from designing semiconductor packages for a few small companies, to doing package designs for top semiconductor companies around the world. From 2014 to 2018, Larry led the expansion of Sarcina beyond package design into final test and wafer sort hardware and software development.

Larry is a semiconductor… Read More

WEBINAR: Chipmakers can leverage generative AI to speed up RTL design and verification

The subjects of Generative AI and Large Language Models (LLMs) permeate businesses and the public conversation. It’s not without good reason! While this emergent field of AI develops, it is now seen at a minimum as a valuable assistant, or, often, a dramatic accelerant to productivity, even to technical workflows.

As we’re … Read More

BDD-Based Formal for Floating Point. Innovation in Verification

A different approach to formally verifying very challenging datapath functions. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always, feedback welcome. We’re planning to add a wrinkle… Read More

Is Intel About to Take Flight?