TSMC announced their Q2 financial results yesterday. Revenue was $5.2B (at the high end of guidance) with net income of $1.6B. This is up 17.4% on Q1 and up 21.6% year-to-year. Gross margin is up too, at 49% which is up 3.2 points on Q1 and 0.3 points year-to-year. As usual the financial results are not directly that interesting since… Read More

Where will Apple Manufacture the next iPhone Brain?

There still seems to be a lot of confusion here so let me set the record straight. In regards to the Apple Ax SoC, the Apple iPhone 5s will have Samsung 28nm Silicon. Samsung 28nm is still ramping but Samsung can make enough wafers and eat the yield issues no problem. The Apple iPhone 6 in 2014 will have TSMC 20nm as I reported previously.… Read More

The Future of Mobile Semiconductor Devices

During my trip to Taiwan I hopped on over to Hong Kong for a speaking engagement. One of the things I do as an “Internationally Recognized Industry Expert” is help the financial world understand the semiconductor landscape as it pertains to SoCs and mobile devices. Usually I do this over the phone or in writing but I prefer to do it in… Read More

TSMC and Xilinx on the FinFAST Track!

The power of the fabless semiconductor ecosystem never ceases to amaze me. On one hand you have the Intel backed press crowing about Intel stealing Altera from TSMC. On the other hand you have Xilinx and TSMC crowing about a new ‘one-team’ approach. If you are interested in the real story you’ve come to the right place.

“Altera’s… Read More

Taiwan Semiconductor Tries To Pull A FinFAST One!

This completely misleading title is from a Seeking Alpha (SA) article, a stock investment version of the National Enquirer. As I mentioned inA Call to ARMs, fame and fortune seeking SA Authors make a penny per click so sensationalism sells. The article is not worth your time so I will save you the click and skip to the misguided conclusion:… Read More

TSMC Goes To DAC

TSMC will be at DAC again this year, of course. The main event, as last year, is the OIP Theater where TSMC’s partners come and present their collaboration stories. Here is the schedule:… Read More

The Morphing of Intel’s Monopoly

It was a generation ago when Intel, less than three years old, created the three fundamental building blocks of the compute era: the DRAM, the EPROM and the Microprocessor, an incredible feat of innovation by any measure. Manufacturing yield, not power or performance determined success of failure and in the first two … Read More

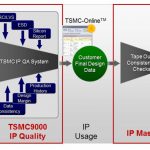

IP Quality: Foundation of a Successful Ecosystem

Talking about Design IP (I mean successful Design IP) lead you to quickly pronounce the two magic key words: Quality and Ecosystem. Those who remember the IP emergence in the mid 90’s know very well why Quality has to be a prerequisite when dealing with Design IP, as they probably have paid the price of mediocre IP quality at that time.… Read More

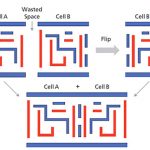

How To Design a TSMC 20nm Chip with Cadence Tools

Every process node these days has a new “gotcha” that designers need to be aware of. In some ways this has always been the case but the changes used to be gradual. But now each process node has something discontinuously different. At 20nm the big change is double patterning. At 14/16nm it is FinFET.

Rahul Deokar and John… Read More

Solido CEO on 20nm/16nm TSMC and GLOBALFOUNDRIES Design Challenges

EDA needs more CEOs like Amit Gupta. Solido, which is now profitable, is his second AMS EDA company. The first, Analog Design Automation (ADA), was purchased by Synopsys for a hefty multiplier. Prior to becoming an EDA entrepreneur, Amit was product manager for the wireless group at Nortel and a hardware engineer for the RF communications… Read More