You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 16126

[name] => Lithography

[slug] => lithography

[term_group] => 0

[term_taxonomy_id] => 16126

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 187

[filter] => raw

[cat_ID] => 16126

[category_count] => 187

[category_description] =>

[cat_name] => Lithography

[category_nicename] => lithography

[category_parent] => 0

[is_post] =>

)

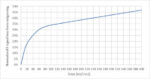

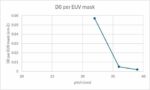

Dosing for EUV lithography walks a fine line between productivity and defectivity. Fabs can choose higher-dose exposures to suppress photon shot noise [1]. However, higher doses require EUV machines to scan the wafer at slower speeds, degrading throughput [2].

On the other hand, there is the threat of resist thickness loss that… Read More

It lays the foundation for the Stochastics Resolution Gap

Chris Mack, the CTO of Fractilia, recently wrote of the “Stochastics Resolution Gap,” which is effectively limiting the manufacturability of EUV despite its ability to reach resolution limits approaching 10 nm in the lab [1,2]. As researchers have inevitably found, … Read More

The relentless miniaturization of semiconductor devices has always relied on achieving ever-smaller features on silicon wafers. However, as the industry enters the realm of extreme ultraviolet (EUV) lithography, it faces a critical barrier: stochastics, or the inherent randomness in patterning at atomic scales. This phenomenon… Read More

The topics of stochastics and blur in EUV lithography has been examined by myself for quite some time now [1,2], but I am happy to see that others are pursuing this direction seriously as well [3]. As advanced node half-pitch dimensions approach 10 nm and smaller, the size of molecules in the resist becomes impossible to ignore for… Read More

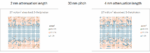

In High-NA EUV lithography systems, the numerical aperture (NA) is expanded from 0.33 to 0.55. This change has been marketed as allowing multi-patterning on the 0.33 NA EUV systems to be avoided. Only very recently have specific examples of this been provided [1]. In fact, it can be shown that double patterning has been implemented… Read More

A comprehensive update to the EUV stochastic image model

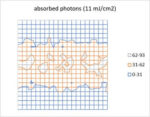

In extreme ultraviolet (EUV) lithography, photoelectron/secondary electron blur and secondary electron yield are known to drive stochastic fluctuations in the resist [1-3], leading to the formation of random defects and the degradation of pattern fidelity at advanced

…

Read More

In a DRAM chip, the memory array contains features which are the most densely packed, but at least they are regularly arranged. Outside the array, the regularity is lost, but in the most difficult cases, the pitches can still be comparable with those within the array, though generally larger. Such features include the lowest metal… Read More

Electron blur, stochastics, and now polarization, are all becoming stronger influences in EUV lithography as pitch continues to shrink

As EUV lithography continues to evolve, targeting smaller and smaller pitches, new physical limitations continue to emerge as formidable obstacles. While stochastic effects have long been… Read More

Two approaches compared

With half-pitch approaching 10 nm, EUV patterning is heavily impacted by stochastic effects, which are aggravated from reduced image contrast from electron blur [1]. A two-mask (“LELE”: Litho-Etch-Litho-Etch) approach was proposed to pattern core features for self-aligned double patterning (SADP)… Read More

Peak probability at zero distance actually makes no sense

In lithography, it is often stated that the best resolution that can be achieved depends on wavelength and numerical aperture (NA), but this actually only applies to the so-called “aerial” image. When the image is actually formed in the resist layer, it also depends on an… Read More

Solving the EDA tool fragmentation crisis