What do genome sequencing, engineering modeling and simulation, and big data analytics have in common? They’re all bandwidth-hungry applications with complex data workloads. High-performance computing (HPC) systems deliver the parallel processing capabilities to generate detailed and valuable insights from these applications.

Semiconductor Intellectual Property

CEO Interview: Kush Gulati of Omni Design Technologies

Kush Gulati is the CEO of Omni Design Technologies, a company he co-founded in 2015 to lead a transformation in how high-performance analog IP is developed and integrated into SoCs in advanced process nodes. With a PhD from MIT, he is a renowned expert in data converters, and a serial entrepreneur. His first startup was a detective… Read More

RISC-V is Building Momentum

The semiconductor intellectual property (SIP) market is an integral part of the semiconductor industry. Third-party IP has propelled the industry, opening the door for many new products from start-ups to established IDMs. Enabling increasingly complex devices, reducing the cost of product development and reducing the time… Read More

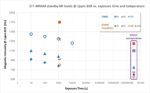

MRAM Magnetic Immunity – Empirical Study Summary

The main threat for the wide adoption of MRAM memories continues to be their lack of immunity to magnetic fields. MRAM magnetic immunity (MI) levels has seen significant research over the years and new data is continuously published from the main MRAM vendors.

This data, however, is rarely compared to magnetic field exposure scenarios… Read More

SoC Integration – Predictable, Repeatable, Scalable

On its face System-on-chip (SoC) integration doesn’t seem so hard. You gather and configure all the intellectual properties (IPs) you’re going to need, then stitch them together. Something you could delegate to new college hires, maybe? But it isn’t that simple. What makes SoC integration challenging is that there are so many… Read More

Why In-Memory Computing Will Disrupt Your AI SoC Development

Artificial intelligence (AI) algorithms thirsting for higher performance per watt have driven the development of specific hardware design techniques, including in-memory computing, for system-on-chip (SoC) designs. In-memory computing has predominantly been publicly seen in semiconductor startups looking to disrupt… Read More

Upcoming Webinar on Resistive RAM (ReRAM) Technology

On-chip memory (embedded memory) makes computing applications run faster. In the early days of the semiconductor industry, the desire to utilize large amount of on-chip memory was limited by cost, manufacturing difficulties and technology mismatches between logic and memory circuit implementations. Since then, advancements… Read More

RIP Jim Hogan – An Industry Icon

An unavoidable consequence of getting older is that more frequently our friends and colleagues unexpectedly leave us for their final venture. Jim Hogan, widely known and loved in the semiconductor industry, has passed on. He will leave a substantial hole in the hearts of many. Always ready with seasoned advice, a sympathetic … Read More

IP and Software Speeds up TWS Earbud SoC Development

The global market for earphones and headphones in 2020 is estimated to have been $34B and is expanding at a compound rate of over 20% per year. Of this almost 50% is said to be earphones which are shifting rapidly to True Wireless Stereo (TWS). We have seen the sales of TWS devices grow from 1M units is 2016 to 109M units in 2019, though … Read More

Quantum Tunneling for OTPs, PUFs: Higher security

I’ve had a number of enjoyable discussions with John East who ran Actel until it was acquired. (John and Actel devices also play an important role in my book, The Tell-Tale Entrepreneur.) This is relevant because Actel were well-known for their anti-fuse FPGAs. eMemory Technology, the subject of this blog, also produce an anti-fuse… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center