Some background. Sonics has been in the network-on-chip (NoC) business for a long time. Nearly 18 years years. When Arteris launched their products, Sonics figured Arteris were infringing Sonics’s patents and in 2011 brought a complaint against them. Details are here. Arteris looked at a couple of their own patents (if… Read More

Semiconductor Intellectual Property

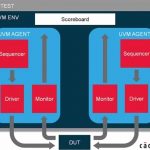

So Easy To Learn VIP Integration into UVM Environment

It goes without saying that VIPs really play a Very Important Part in SoC verification today. It has created a significant semiconductor market segment in the fabless world of SoC and IP design & verification. In order to meet the aggressive time-to-market for IPs and SoCs, it’s imperative that readymade VIPs which are proven… Read More

A song of optimization and reuse

If you hang around engineers for any time at all, the word optimization is bound to come up. The very definition of engineer is to contrive or devise a solution. With that anointing, most engineers are beholden to the idea that their job is creating, synthesizing, and perfecting a solution specifically for the needs of a unique situation.… Read More

PCI Express 4 specification just released for PCI-SIG DevCon

I have been alerted by a blog from Moshik Rubin from Cadence: PCI-SIG has finally released the PCIe 4.0 rev 0.3 specification for members’ review, on time for the PCI-SIG developers conference last June in Santa Clara. Since the early days of PCI Express in 2005, Denali (at that time, now Cadence) has positioned the PCIe VIP… Read More

I’ll be with you in a second

One aspect of always-on is power conservation, being able to respond to events without having a device constantly in full-power mode. This month, the announcement of the Amazon Fire Phone and details revealed about the Google Android Wear SDK suggest another important dimension: the competitive advantage of rapid, frictionless… Read More

ARC EM DSP supports Always-on Devices

The ARC EM family is the low-power, embedded and low footprint processor part of the larger ARC processor. To target the ultra low-power markets like wearable and IoT, Synopsys has added DSP capabilities to EM5D and EM7D. To be specific, these cores are optimized for ultra low-power control and DSP, thanks to:

- Energy-efficient

Getting the best from a Radio Spectrum: MIMO

Exchanging data through wireless network is that we are doing every day, every hour if not every minute. Not only we use our smartphone to discuss or exchange Emails, but also to download, or upload, massive amounts of data. Thus, the radio spectrum has become to be busy, and is an expansive piece for carriers. Optimizing this radio… Read More

Always-on and the new wearable core

Recently, I mentioned smartphone SoCs consume one, maybe two orders of magnitude too much power for broader use in wearables. However, that is only when they are “on”. To save power and stretch battery life, smartphones spend a lot of time napping – display off, sitting still with MEMS sensors powered down, waiting for an incoming… Read More

Sidense NVM IP clears TSMC9000 at 28nm

Maybe I’ve spent too many years whiffing solder flux fumes and absorbing doses of X-band radiation in anechoic chambers, but I’m a firm believer in the axiom: “Give me enough engineers, and I can get 10 of anything to work right, once.” We have to make this … fit into this … using only this stuff … is what legends are made of.… Read More

Dark Silicon

One of the problems with chips today is that of so-called “dark silicon”. We can put massive functionality on an SoC today. A billion transistors, and that is just at 28nm. But power constraints (both leakage and dynamic power) limit how much of the chip can be powered up at any one time. In some cases this is not that big… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!