In a move that underscores the semiconductor industry’s push toward resilient supply chains and agile innovation, Thalia Design Automation and X-FAB Silicon Foundries have announced a strategic partnership aimed at safeguarding supply continuity and accelerating intellectual property (IP) migration. This collaboration,… Read More

Semiconductor Intellectual Property

AI Everywhere in the Chip Lifecycle: Synopsys at AI Infra Summit 2025

At the AI Infra Summit 2025, Synopsys showed how artificial intelligence has become inseparable from the process of creating advanced silicon. The company’s message was clear: AI is an end-to-end engine that drives every phase of chip development. Three Synopsys leaders illustrated this from distinct vantage points. Godwin… Read More

Analog Bits Steps into the Spotlight at TSMC OIP

The TSMC Open Innovation Platform (OIP) Ecosystem Forum kicked off on September 24 in Santa Clara, CA. This is the event where TSMC recognizes and promotes the vast ecosystem the company has created. After watching this effort grow over the years, I feel that there is nothing the group can’t accomplish thanks to the alignment and… Read More

Yuning Liang’s Painstaking Push to Make the RISC-V PC a Reality

At Embedded World 2025 in Nuremberg, Germany, on March 11, 2025, Yuning Liang, DeepComputing Founder and CEO walked onto the stage with a mischievous smile and a challenge. “What’s the hardest product to make?” he asked rhetorically. “A laptop. It’s bloody hard… but we did it. You can swap the motherboard, you can upgrade, you can’t… Read More

Arm Lumex Pushes Further into Standalone GenAI on Mobile

When I first heard about GenAI on mobile platforms – from Arm, Qualcomm and others – I confess I was skeptical. Surely there wouldn’t be enough capacity or performance to deliver more than a proof of concept? But Arm, and I’m sure others, have been working hard to demonstrate this is more than a party trick. It doesn’t hurt that foundation… Read More

SiFive Launches Second-Generation Intelligence Family of RISC-V Cores

SiFive, founded by the original creators of the RISC-V instruction set, has become the leading independent supplier of RISC-V processor IP. More than two billion devices already incorporate SiFive designs, ranging from camera controllers and SSDs to smartphones and automotive systems. The company no longer sells its own chips,… Read More

The IO Hub: An Emerging Pattern for System Connectivity in Chiplet-Based Designs

In chiplet-based design we continue the march of Moore’s Law by scaling what we can put in a semiconductor package beyond the boundaries of what we can build on a single die. This style is already gaining traction in AI applications, high performance computing, and automotive, each of which aims to scale out to highly integrated … Read More

Exploring Cycuity’s Radix-ST: Revolutionizing Semiconductor Security

Cycuity’s Radix-ST represents a groundbreaking advancement in semiconductor security, addressing the growing complexity and vulnerability of modern chip designs. Introduced on August 27, 2025, by Cycuity, Inc., Radix-ST leverages static analysis techniques to identify and resolve security weaknesses early in the chip… Read More

CEO Interview with Rabin Sugumar of Akeana

Rabin Sugumar was Distinguished Engineer and Chief Architect at Marvell/Cavium and built and led the architecture group for the ThunderX Arm server processor line. Most recently he led the architecture of the ThunderX3 processor, which had industry leading single thread performance and socket level performance at time of … Read More

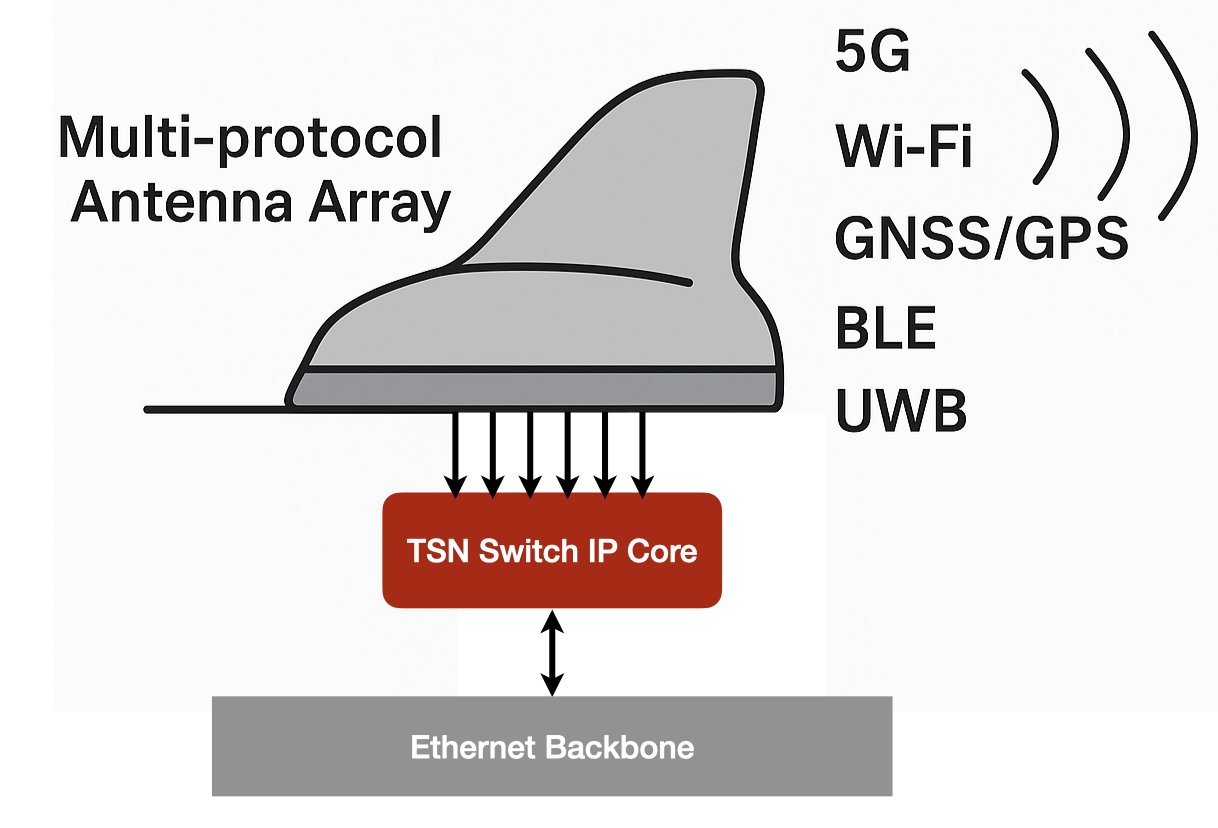

RANiX Employs CAST’s TSN IP Core in Revolutionary Automotive Antenna System

This press release from CAST announces a significant collaboration with RANiX Inc., highlighting the integration of CAST’s TSN Switch IP core into RANiX’s new Integrated Micro Flat Antenna System (IMFAS) SoC. This development underscores the growing adoption of Time-Sensitive Networking (TSN) in the automotive… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!