When we first started talking about “smart”, as in smart cars, smart homes, smart cities and the like, our usage of “smart” was arguably over-generous. What we really meant was that these aspects of our daily lives were becoming more computerized and connected. Not to say those directions weren’t useful and exciting, but we weren’t… Read More

Semiconductor Intellectual Property

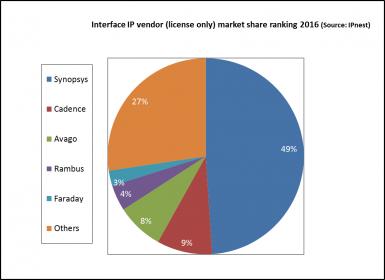

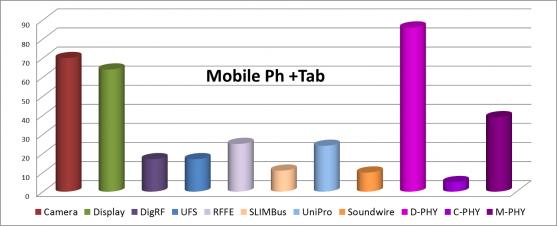

Worldwide Interface IP Revenue Grew by 13.5% in 2016 (Source: IPnest)

IPnest has released the 9[SUP]th[/SUP] version of the Interface IP Survey, ranking by protocol the IP vendors addressing the Interface segments: USB, PCI Express, (LP)DDRn, MIPI, Ethernet & SerDes, HDMI/DP and SATA. When the 1[SUP]st[/SUP] version has been issued in 2009, the IP segment was weighting $225 million and the… Read More

7nm SERDES Design and Qualification Challenges!

Semiconductor IP is the fastest growing market inside the fabless ecosystem, it always has been and always will be, especially now that non-traditional chip companies are quickly entering the mix. Towards the end of the year I always talk to the ecosystem to see what next year has in store for us and 2018 looks to be another year of … Read More

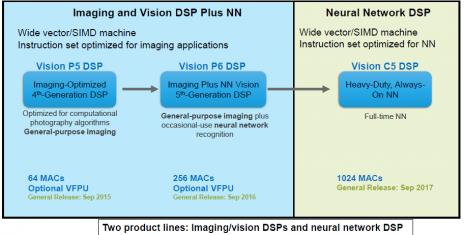

Tensilica Vision P6 DSP is Powering Huawei Kirin 970 Image

Cadence has recently announced two key design-in for their Vision DSP IP family: MediaTek’s Helio P30 integrates the Tensilica Vision P5 DSP and HiSilicon has selected the Cadence® Tensilica® Vision P6 DSP for its 10nm Kirin 970 mobile application processor. The Kirin 970 being integrated into Huawei’s new Mate 10 Series mobile… Read More

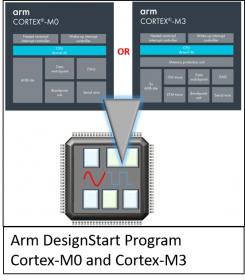

Arm and Mentor Use DesignStart Program to Accelerate Proof-of-Concept for IoT Designs

Sometimes the hardest thing about bringing a new idea to fruition is overcoming the inertia to get started with a proof-of-concept. You must be able to put together enough parts of the solution to prove to those controlling budgets that an idea has merit and is worth taking to the next level. It’s a bit of a chick-vs-egg scenario as … Read More

Finding the Right Needle in the IP Haystack

As the percentage of pre-configured IP increases in semiconductors, so design teams are able to reduce design cycle times. But one of the challenges for design teams is the inability to quickly and easily find IP because it’s incorrectly classified, sat in a designer’s home directory, or it’s been put into the ‘repository’ by an… Read More

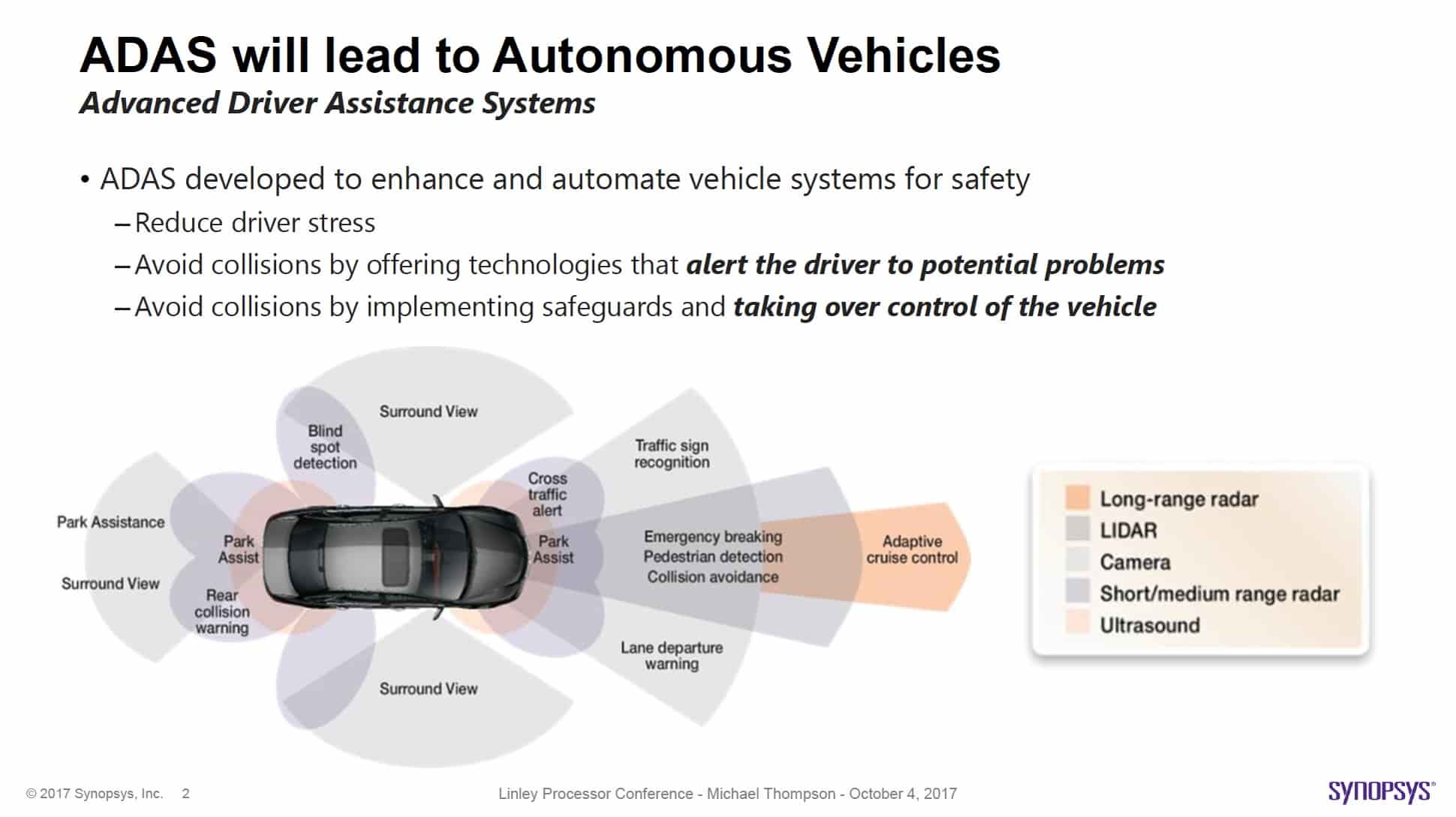

High performance processor IP targets automotive ISO 26262 applications

The reason you are seeing a lot more written about the ISO 26262 requirements for automotive electronics is, to put it bluntly, this stuff is getting real. Driver assist systems are no longer only found in the realm of Mercedes and Tesla, almost every car in every brand offers some driver assist features. However, the heavy lifting… Read More

VESA DSC Encoder Enables MIPI DSI to Support 4K resolutions

Some of the MIPI specifications are now massively used in mobile (smartphone), like the Multimedia related specs, Camera Serial Interface (CSI-2) and Display Serial Interface (DSI). These specifications are now adopted inautomotive infotainment systems, and augmented reality (AR)/ virtual reality (VR) devices. If you … Read More

DesignShare is all About Enabling Design Wins!

One of the barriers to silicon success has always been design costs, especially if you are an emerging company or targeting an emerging market such as IoT. Today design start costs are dominated by IP which is paid at the start of the project and that is after costly IP evaluations and other IP verification and integration challenges.… Read More

12 Year-old Semiconductor IP and Design Services Company Receives New Investment

I have a transistor-level IC design background so was intrigued to learn more from the CEO of an IP and services company that started out in India 12 years ago. Last week I spoke with Samir Patel, CEO of Sankalp Semiconductorabout the newest $5 million financial investment in his company from Stakeboat Capital Fund. The Stakeboat… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era