If integrating an embedded FPGA (eFPGA) into your ASIC or SoC design strikes you as odd, it shouldn’t. ICs have been absorbing almost every component on a circuit board for decades, starting with transistors, resistors, and capacitors — then progressing to gates, ALUs, microprocessors, and memories. FPGAs are simply one more… Read More

When FPGA Design Looks More Like ASIC Design

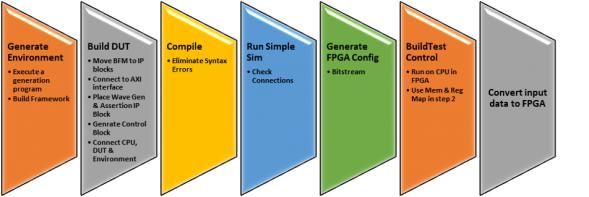

I am sure there are many FPGA designers who are quite content to rely on hardware vendor tools to define, check, implement and burn their FPGAs, and who prefer to test in-system to validate functionality. But that approach is unlikely to work when you’re building on the big SoC platforms – Zynq, Arria and even the big non-SoC devices.… Read More

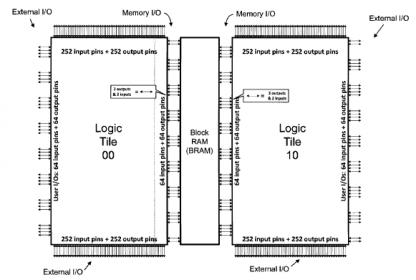

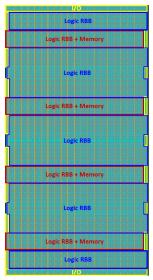

Block RAM integration for an Embedded FPGA

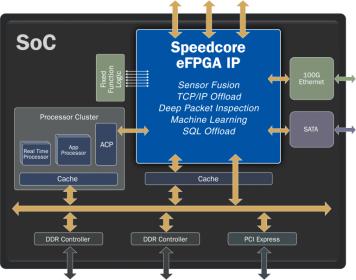

The upcoming Design Automation Conference in San Francisco includes a very interesting session –“Has the Time for Embedded FPGA Come at Last?” Periodically, I’ve been having coffee with the team at Flex Logix, to get their perspective on this very question – specifically, to learn about the key features that customers are seeking… Read More

Hard IP for an embedded FPGA

As Moore’s Law enables increased integration, the diversity of functionality in SoC designs has grown. Design teams are seeking to utilize outside technical expertise in key functional areas, and to accelerate their productivity by re-using existing designs that others have developed. The Intellectual Property (IP) industry… Read More

Achronix Momentum Building with Revenue Growth, Product/Staff Expansion, New HQ

5G Wireless, Network Acceleration, Data centers, Machine Learning, Compression, Encryption fueling the Growth

Building on its increasing momentum, Achronix Semiconductor Corporation held a ribbon-cutting ceremony on Tuesday, April 25, with the presence of Santa Clara’s Mayor Lisa Gillmor, customers, and partners, employees… Read More

RDC – A Cousin To CDC

In a post-silicon bringup, it is customary to bring the design into a known state prior to applying further testing sequences. This is achieved through a Power-on-Reset (POR) or similar reset strategy which translates to initializing all the storage elements to a known state.

During design implementation, varying degrees of… Read More

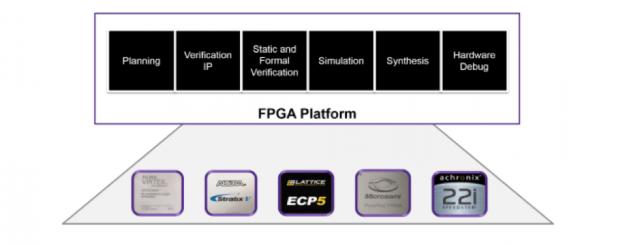

The 4th Way Beyond Simulation, FPGA Synthesis, and Emulation

As verification continues to be a key ingredient in successful design implementation, new approaches have been tried to balance cost, time to results and comprehensive analysis in designs that require large patterns in some application like Image Processing. Simulation environments are well proven, and designers tend to … Read More

Configurability for Embedded FPGA Hard IP

IP providers need to evaluate several complex engineering problems when addressing customer requirements – perhaps the most intricate challenge is the degree of IP configurabilityavailable to satisfy unique customer applications. … Read More

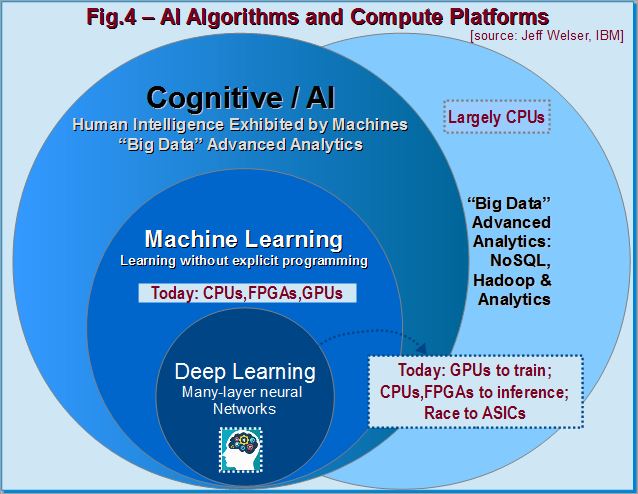

FPGA, Data and CASPA: Spring into AI (2 of 2)

Adding color to the talks, Dr. Jeff Welser, VP and IBM Almaden Research Lab Director showed how AI and recent computing resources could be harnessed to contain data explosion. Unstructured data growth by 2020 would be in the order of 50 Zetta-bytes (with 21 zeros). One example, the Summit supercomputer developed by IBM for use at… Read More

FPGA, Data and CASPA: Spring into AI

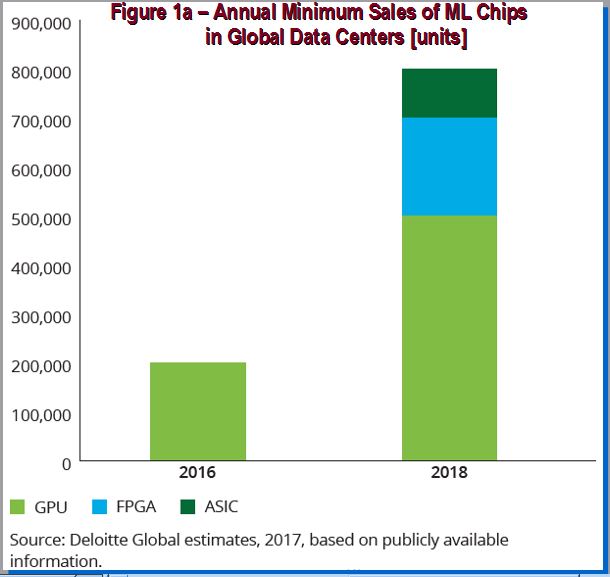

Just like good ideas percolate longer, we have seen AI adoption pace picking-up speed, propelled by faster GPUs. Some recent data points provide good indication that FPGA making a comeback to bridge chip-design needs to keep-up with AI’s ML applications.

According to the Deloitte research firm there is a projected increase of… Read More

The Name Changes but the Vision Remains the Same – ESD Alliance Through the Years